4 次 VCF CEM3320/V3320 (2)

ゲインセル部分を 1 次ハイパスフィルタとして動作させる接続を下に示します。

ローパスフィルタではゲインセル回路の基本構成に対して 2 本の抵抗の追加が必要でしたが、ハイパスフィルタでは回路は基本のままで、接地していた側のコンデンサの端子から信号を入力します。

信号はコンデンサを介して入力されるので、前段の出力信号に DC 成分が乗っていてもカットされます。 そのため、前段出力の DC 成分の有無にかかわらず、バイアス電流補正のための抵抗は必要ありません。

オールパスフィルタの場合の接続を下に示します。

LPF と HPF の重ね合わせに相当し、前段の出力信号を抵抗 RC を介してと、コンデンサを介してとの両方から入力します。

前段が別のゲインセルで、出力信号に DC が乗っている場合には LPF 構成と同様にバイアス電流の補正のための抵抗 RB が必要です。

バンドパスフィルタは最低でも 2 次になるので、1 次フィルタ単独では実現できず、 1 次 LPF → 1 次 HPF、あるいは 1 次 HPF → 1 次 LPF の順に縦続接続して実現します。

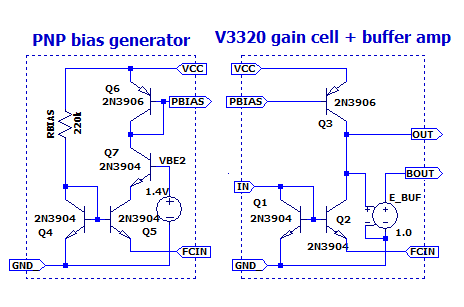

このゲインセルおよびバッファ・アンプ部の spice モデルの回路を下に示します。 LTspice XVII を使用しています。

DC バイアスによる動作点の決定と、AC 特性を見ることだけに注力しており、他の特性については考慮していません。 簡単のため、バッファ・アンプ部はゲイン 1 の「E」エレメント (電圧制御電圧源) を使っています。

図の左側がゲインセル部分のソース電流側を受け持つ PNP トランジスタ (Q3) のベースバイアスを発生させる回路で、複数のゲインセル回路で共用します。

Q7 はカスコード・トランジスタで、Q4 / Q5 のカレントミラー出力電流がアーリー効果により設定値からずれるのを防ぐために挿入したものです。 Q7 がなくてもゲインセル部分のバイアス電流が設定値からずれるだけで、信号のパスには影響しないので、ずれを気にしなければ省略可能です。

この回路を LTspice の機能で net list に変換し、手作業で編集してサブサーキットに仕立てたものを下に示します。

* X:\wsp2\LTS\v3320_subckt.asc * CEM3320/V3320 gain cell + unity gain buffer * * input * | PNP_bias_in * | | curr_out = vbuf_in * | | | gnd * | | | | vbuf_out * | | | | | freq_CV_in * | | | | | | Vcc * | | | | | | | .subckt V3320_GM IN PBIAS OUT GND_ BOUT FCIN VCC * * gain cell * Q1 IN IN GND_ 0 2N3904 Q2 OUT IN FCIN 0 2N3904 Q3 OUT PBIAS VCC 0 2N3906 * * unity gain voltage buffer * E_BUF BOUT GND_ OUT GND_ 1.0 .ends V3320_GM * PNP bias generator * * PNP_bias_out * | gnd * | | freq_CV * | | | Vcc * | | | | .subckt V3320_PBIAS PBIAS GND_ FCIN VCC * Q6 PBIAS PBIAS VCC 0 2N3906 RBIAS VCC N002 220k Q4 N002 N002 GND_ 0 2N3904 Q5 N003 N002 FCIN 0 2N3904 Q7 PBIAS N001 N003 0 2N3904 * * base bias for cascode NPN Tr. * VBE2 N001 GND_ 1.4V .ends V3320_PBIAS * 2N3904/2N3906 model * .lib standard.bjt

このファイルの名称を「V3320_gm.sub」とし、このサブサーキットを引用して使う本体の「.asc」ファイルと同じフォルダに入れておきます。

ゲインセル部分の入出力特性を見るシミュレーションの回路を下に示します。

「裸」のゲインセル特性を見るためフィードバックをかけていないので、そのままでは動作点が定まりません。 そのため、「OUT」端子を電圧制御電圧源「E_CLAMP」により 0.46 VCC にクランプしています。 OUT 端子と E_CLAMP の間を流れる電流をモニタし、プロットしています。

結果のグラフを下に示します。

入力電圧「VIN」を DC スイープで -8 V から +8V まで振っており、それが横軸になっています。

また、パラメタとして周波数 CV 入力「FCIN」を -18.2 mV から +163.8 mV まで 18.2 mV ステップで変化させています。

FCIN = -18.2 mV が周波数最大 = ゲインセル電流最大 (赤色のトレース) で、ステップがひとつ進むごとに電流は半減していき、FCIN = 163.8 mV で周波数最小 = ゲインセル電流最小となっています。

青色のトレースが FCIN = 0 mV の場合で、出力電流は 64 μA 近辺で頭打ちになっています。 これは、VIN がマイナスになってゲインセルのシンク側 (NPN) の電流が絞られてほぼゼロになり、ソース側 (PNP) の定電流源のみが寄与する状態となるためです。