V2164 の特性測定 (3)

SSM2164 の回路構成に何か名前が付いていないかを調べていたら、同様の構成を持つ SSM2014 / SSM2018 / SSM2118 のデータシートに「Frey Operational Voltage Contorolled Element」(略称は「OVCE」、「Frey」は人名) という記述を見つけました。

「OVCE」という単語は SSM2164 のデータシートには登場しません。

SSM2018 などは 16 ピン DIP パッケージに1回路しか内蔵されていませんが、外部の接続により、VCA だけでなく、いろいろな機能を実現できるようになっています。

そういった意味で「Element」という語が使われているのなら、VCA 単機能である SSM2164 は「Element」ではなく、「OVCE」と呼ばれないのかも知れません。

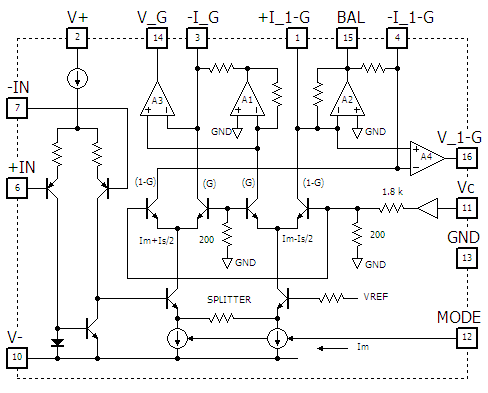

SSM2018 の一部簡略化したブロック・ダイアグラムを下に示します。

「一部簡略化」というのは、ゲイン変化に応じて位相補償量を変える回路が内蔵されているのですが、それの記述を省略したということです。

ゲインセル部分の差動電流出力をシングルエンドの電圧に変換する I-V 変換用の OP アンプが内蔵されていて、出力は電圧で得られます。

コントロール入力 Vc にはバッファが挿入されており、入力インピーダンスは 1 MΩ と高くなっています。

仮定として、V2164 にも Vc バッファが付いていて、そのバイアス電流がソース方向なら前回の測定のような結果が得られるかも知れませんが、その可能性は低いと思います。

VCA 機能を実現するための外部回路を含んだ構成を下に示します。

OP アンプ「A3」のフィードバック抵抗として、点線で囲って示した 18 kΩ の抵抗を外付けします。

そのほか、いくつかのピン間を接続する必要がありますが、ピンの表示は省略して、回路図内で直接に接続してあります。 トリミングのための接続も省略してあります。

同相入力、反転入力が同時に得られ、差動入力としても使えます。 同相入力、反転入力のいずれかだけが必要な場合は、必要ない側の抵抗とコンデンサを取り去ってオープンにします。

この「Frey Operational Voltage Contorolled Element」をググっていて、

US Patent 4,823,093

"DYNAMICALLY BIASED VOLTAGE CONTROLLED ELEMENT"

を見つけました。 発明者はもちろん Douglas R. Frey 氏です。

この特許の中に数種類の回路例が示されており、その中には Blackmer セルを使った実現例もありました。

「Blackmer セル」は houshu さんのブログで初めて知ったので、その予備知識がなければ分からなかったと思います。

V2164 が実は Blackmer セルで実現されており、PNP 側のベース電流が大きければ入力バイアス電流がソース方向になる可能性もありますが、それはちょっと考えにくいです。

特許の中には、前のブロック・ダイアグラムでは省略した、ゲイン変化に対応して位相補償量を可変する回路についての記述や、差動ペアのベース電流の補償のための回路の記述も含まれています。

ただし、「ベース電流補償」という表現ではなく、「AB 級動作時の歪を補償する回路」のような表現になっています。

これはかなり有力で、V2164 にも、このような補償回路が入っている可能性はかなり高いと思います。

ただし、この特許に示されている方法そのままでは、シンク電流方向の NPN トランジスタのベース電流に、補償回路のシンク電流を加えて、ベース抵抗を流れるバイアス電流を均等化するので、結局、バイアス電流はシンク方向のままです。

この補償回路の考えに基づき、補正電流の向きをソース方向にして、ベース電流を打ち消す方向に作用させるのは SSM2018 の回路ではやりにくいですが、SSM2164 の回路では難しくありません。

補償回路の詳細については、次回以降の記事で触れます。