3V単一電源動作の VCF (9) - Minimoog 回路のシミュレーション (5)

今回は、トランジスタ・ラダー構成で、1次の (電圧可変) オールパス・フィルタ (APF) を実現します。

4次 LPF 特性を実現できるトランジスタ・ラダー回路を使いながら、まともに実現できるのは1次 APF 特性に過ぎないので、ここまで来ると、かなり無理やりな感じです。

前回まで、バッファ付き1次 LPF 回路のコンデンサ側から (バッファを通して) 信号を入力すると HPF 特性なると述べてきましたが、それでは、抵抗側とコンデンサ側の両方から信号を流し込むと、どういう特性になるでしょうか。

まず考え付くのは下の図のように、両方とも +1 のバッファを使う方法です。

この場合、抵抗の両端と、コンデンサの両端の電位は常に等しく、抵抗にもコンデンサにも電流は流れません。

出力バッファの入力電圧は、入力バッファの出力電圧に等しく、ゲインは常に 1 という、「素通し」状態で、フィルタとしては役に立ちません。

次は、上の図のように、コンデンサ側を反転して「-1 倍」とする方法です。

コンデンサがオープン状態と見なせる DC 付近の周波数では、抵抗側から入力される「+1 倍」入力のみ有効となりますから、ゲインは 1 で位相遅れはゼロです。

コンデンサがショート状態と見なせる高い周波数域では、コンデンサ側から入力される「-1 倍」入力のみ有効となり、ゲインは 1 で位相遅れが 180°という状態です。

その中間の周波数域では、ゲインは 1 で、位相のみ回るという、一次 APF の特性となります。

LTSpice で理想モデルのシミュレーションをしてみました。

コンデンサ側には「AC -1 V」の電圧源をつないで、逆位相の入力を実現しています。

また、1次 APF を2段接続したものを近似的に実現する出力 (OUT2) を設けています。

正式に1次 APF を2段接続するためには、「OUT1」出力を取り出して、次段のコンデンサ側に入力する必要がありますが、これは、実際の回路では OUT1 出力を取り出すために差動増幅回路を設ける必要があるということになります。

その回路の追加を嫌って、1段目でフェーズシフトされている OUT1 の代用として、もともとの入力を2段目に入れています。

2段目ではコンデンサの容量を1段目の 1/10 とし、1段目での位相シフト量が 180°近くに達する高い周波数の領域で2段目のフェーズシフトが行われるようにします。

2段目には、ほぼ 180°位相が回っている信号が入力されますから、コンデンサ側に入力すべき信号は「AC 1 V」となります。

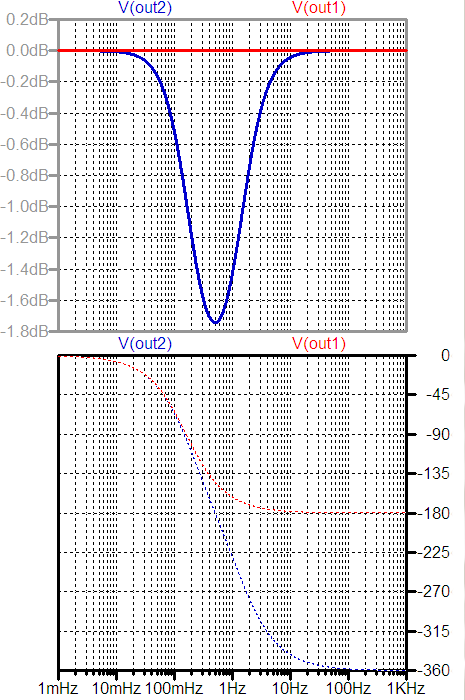

LTSpice でのシミュレーション結果の周波数特性のグラフを次に示します。 上のグラフがゲインで、下のグラフが、点線でプロットされていて、ちょっと見にくいのですが位相のグラフです。

赤色のプロットが1段目の出力で、青色のプロットが2段目の出力です。

1段目の出力は、ちゃんとした1次 APF の特性ですが、2段目の特性は途中のゲインが約 -2 dB 落ち込んでいて、「オールパス」とは言えないものになっています。

2段目のコンデンサの容量を小さく選ぶと、ゲインの落ち込みは少なくなりますが、位相特性の直線性が悪くなります。

前回の Minimoog 回路を2次フィルタの構成にした回路に、さらに変更を加え、1次 APF を実現した回路を下に示します。

一番上のラダー段は、コンデンサを取り去ってフィルタの機能を持たせず、出力の取り出し専用にしてあります。

信号入力は、下の差動段と、ラダー1段目の反転入力側のベースに入力してあります。

LTSpice でのシミュレーション結果の周波数特性のグラフを次に示します。

数十 Hz 以下の周波数の領域でゲインが落ちているのは、例によって、差動増幅部の入力部分の HPF によるものです。

HPF ですから、位相は「進み」特性となり、DC 付近で +90°となります。

また、カットオフ周波数が低い、つまり、テイル電流の小さい場合に全域でゲインが数 dB 落ちているのは、これも毎度おなじみの差動増幅部の入力インピーダンスによる影響です。

数十 kHz 以上の周波数領域で、テイル電流の小さい場合にゲインが落ちているのは、差動増幅部の入力インピーダンスが高域で低下する影響です。

LPF として使う場合には、この領域では十分にゲインが落ちているので、これまで特性には表れていませんでした。

差動増幅部に要求される、約 40 dB というゲインは、特に高性能ではない汎用の OP アンプでは実現が苦しい値です。

仮にゲイン・バンド幅 (GBW) が 1 MHz とすると、20 kHz では裸のゲインが 50 倍 (34 dB) まで低下し、仕上がりのゲインとして 100 倍は実現できないことになります。