3V単一電源動作の VCF (1)

「Analog2.0」の作者の Gan さんが、ブログ「Gaje」で Analog2.0 最後のモジュール VCF の設計が固まったことを報告してらっしゃいます。

OTA 使用のタイプから設計変更した回路はまだナイショということですが、VCF 基板の写真を見れば、一目で Moog タイプのトランジスタ・ラダー・フィルタと分かります。

基板の写真をながめていて、「ネタ」半分ではありますが、乾電池2本分の 3 V 単一電源で動く VCF が作れないかと考え始めました。

ベース結合アンチログ回路の基本部分は の 2 個分 + α で動きますから、基本的に低電圧動作が可能です。

一方、Moog タイプのトランジスタ・ラダー・フィルタは、トランジスタが縦積みになっていますから電源電圧は高くなりがちです。

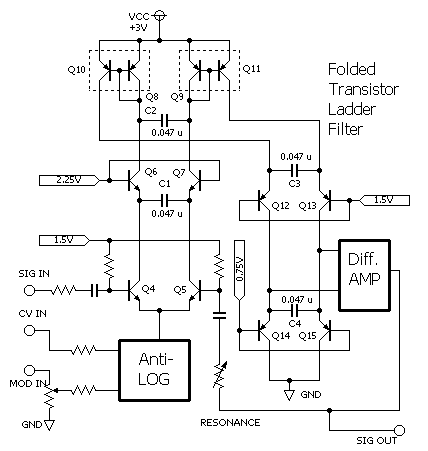

現在考えている回路のブロック・ダイアグラムを下に示します。

アンチログ部と差動増幅部はブロックで表現し、トランジスタ・ラダー部のみ回路を示しています。

動作原理は単純で、NPN トランジスタ・ラダーを積み上げていくと電源電圧が足りなくなってきますから、 側で PNP トランジスタによるカレントミラーで電流を GND 側に折り返し、下に向かって PNP トランジスタ・ラダーを積んでいくものです。

「フォールデッド・トランジスタ・ラダー・フィルタ」 (Folded Transistor Ladder Filter) と呼ぶことにします。

トランジスタの を 0.7 V 程度に見積もると、3 V 単一電源では 4 個まで

を積み上げられることになります。

具体的には 3 / 4 = 0.75 V ですから、トランジスタ1段あたりの = 0.75 V、実際の

が 0.6 V 程度と考えると、

= 0.15 V となり、 p-p 値で 200 mV 程度なら飽和の心配をせずに扱えることになります。

アンチログ出力部では をひとつ消費しますから、残りは 3 個です。

音声信号を入力する差動ペア (Q4, Q5) で1個消費、ラダー1段分 (Q6, Q7) でもう1個消費します。

ここで残り1個となってしまいますから、ここに基本型のカレントミラー (Q8, Q9, Q10, Q11) を置くしかありません。

しかし、基本型のカレントミラーの入力側、つまりダイオード接続された PNP トランジスタ (Q8, Q9) にもコンデンサを接続して、ラダーフィルタ1段分として動作するようにしています。

カレントミラーを構成するトランジスタのマッチングは、回路図で点線で囲った中の2つ (Q8-Q10 ペアおよび Q9-Q11 ペア) について行います。 Q8-Q9、Q10-Q11 のペアではありません。

カレントミラーで電流の向きを反転した後は、PNP トランジスタ・ラダー2段を通ります。 Q14, Q15 のコレクタと GND との間には、まだ 1個分の余裕があります。

Q14, Q15 のエミッタから差動で信号出力を取り出します。

差動増幅部では電源電圧が 3 V と低いので、出力信号の振幅を確保するのは大変です。

抵抗負荷のトランジスタ差動ペアによるアンプでは、出力は p-p 値で ふたつ分程度が精一杯です。

フルスイング出力 (出力レイル・ツー・レイル) の OP アンプを使用した回路にすれば、最大 3 V p-p までは出せますが、VCF を発振させた状態で振幅を安定させるためには、トランジスタ差動増幅回路のソフトクリップ特性 ( 特性) が必要なので、何らかの方法でクリップ特性を持たせる必要があります。

回路の動作については、LTSpice 上で AC 解析を行い、フィルタとして動作することは確かめてあります。

実用的なものになるかどうかは分かりませんが、実際に回路を組んでみて、動作を確認する実験をするつもりです。