PX-150 (16)

今回は CMOS アナログスイッチによる回路です。

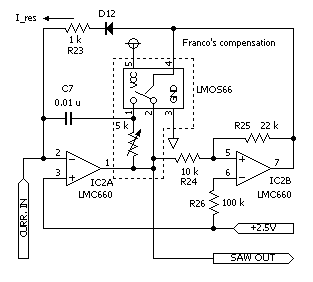

下の回路図のように、当初はワンゲート CMOS ロジック (0.95 mm あるいは 0.65 mm ピッチの 5 ピン・パッケージに CMOS ロジックを1回路のみ内蔵したもの) の TC4S66F を使った回路を試したのですが、アナログスイッチの ON 抵抗が大きく、それによる電圧降下が目立ったので、通常の 74HC シリーズの 74HC4066 に変更して実験を進めました。

東芝 TC4S66F は、スペック上は、メタルゲート CMOS である 4000 ファミリに相当していますが、アナログスイッチの ON 抵抗は 4066 よりは小さく、5 V 電源、25 ℃での標準値では 290 Ω となっています。

74HC シリーズに相当する TC7S66F では、4.5 V 電源、25 ℃での ON 抵抗の標準値は 192 Ω です。

TC7S66F の電源電圧範囲は通常の 74HC シリーズより広く、2 〜 12 V となっています。

ちなみに、TC4S66F (現品表示は「C9」) は新たに購入したものではなく、古い CD-ROM/CD-R ドライブの基板から外したものです。 おなじ基板上に TC7S66F (現品表示は「E9」) もあったのですが、こちらは外すのを失敗してしまいました。

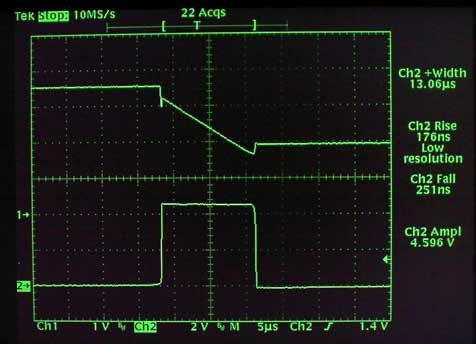

OP アンプに MC14577 を使用し、TC4S66F を使って撮影した波形写真を下に示します。

上の写真は、入力電流が小さい場合で、リセット期間にアナログスイッチの ON 抵抗による電圧降下による「落ち込み」が見られます。

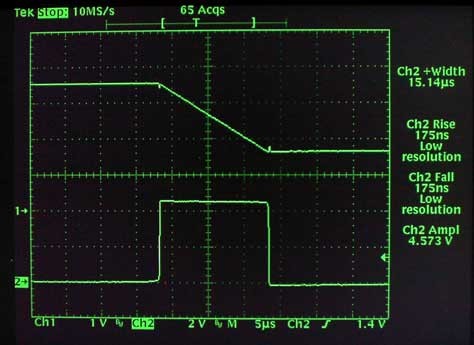

ON 抵抗が標準値で 50 Ω である、通常の 74HC4066 に変えて波形を見ると、まだ少し落ち込みが見られたので、2回路分を並列にしてみた結果が下の写真です。

スパイク状のトランジェントは見られますが、リセット期間の両端でのレベル差は、ほとんど見られなくなりました。

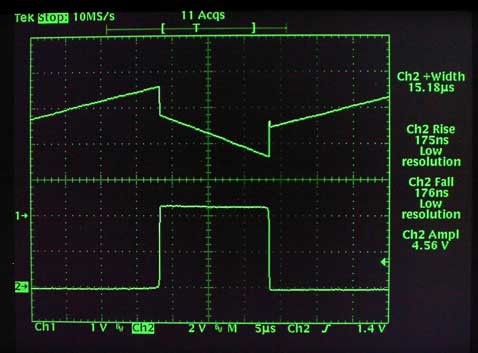

大電流領域での波形を下に示します。

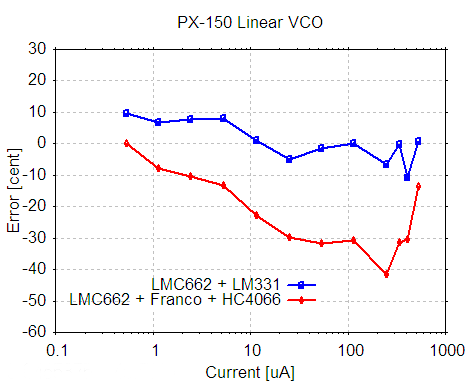

測定結果ですが、リニアスケールでの表示は、前回の単体 FET での結果とほとんど重なるので省略し、セント単位での誤差のグラフのみ示します。

前回に比べて、補正量が多くなるような調整を行いましたが、結果としては大電流領域の誤差が減少するだけで、中電流領域で「ダラ下がり」になっている誤差は減っていないようです。

前回、前々回と、調整次第で誤差量をもっと少なく追い込めるだろうと書きましたが、この「ダラ下がり」の誤差は、現在は考慮していない別の要因によるものかも知れません。

その場合でも、このグラフで直線で表されるような誤差の出方に調整できれば、アンチログ回路でのオクターブ・スパンの調整で直線性を改善できると思います。