PX-150 (15)

前回は、2端子スイッチング素子であるダイオードを使って、積分コンデンサに直列に接続する抵抗を、電流の向きによりスイッチングする回路を扱いました。

それに対し、今回は、3端子のスイッチング素子を使い、コントロール信号によって ON/OFF を切り換える回路について考えます。

単体の3端子スイッチング素子として一般的なのは、バイポーラ・トランジスタと FET がありますが、FET の方が回路が簡単になるので、ここでは FET だけを扱います。

集積回路としては、CMOS アナログスイッチがありますが、それは次回の記事で触れます。

まず、コントロール信号として、コンパレータ出力を使います。

出力フルスイングの OP アンプの使用を仮定すると、リセット期間、つまりスイッチ ON するべき期間で 5 V、それ以外、つまり、スイッチ OFF すべき期間で 0 V という電圧レベルになります。

このコントロール信号の極性から、N チャネル FET を使用して、ゲートはコンパレータ出力に接続し、ソース/ドレインを抵抗の両端に接続することが決まります。

のこぎり波の電圧としては、上端は 3.6 V 程度、下端は 1.4 V 程度ですから、

- のこぎり波上端

で

は

から

に変化

- のこぎり波下端

で

は

から

に変化

することが分かります。

つまり、FET が ON すべきリセット期間では = 1.4 〜 3.6 V、OFF すべき期間では

= -1.4 〜 -3.6 V となりますから、ディプリーション特性のジャンクション FET でも、エンハンスメント特性の MOS FET でも使用できることになります。

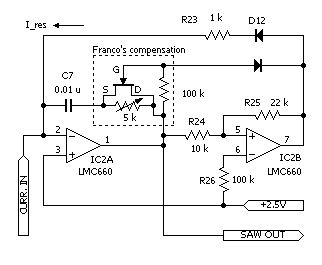

N ch J-FET 使用の回路を下に示します。

ジャンクション FET ではゲート・ソース間が順バイアスされるとゲート電流が流れてしまいますから、ダイオードを挿入してゲート電圧が正になることを防ぎます。

このダイオードの順方向電圧降下分の約 0.6 V により、 = -0.8 V 程度に目減りしてしまいますから、使用する J-FET は、このゲート電圧で十分 OFF にならなければいけません。

また、 は約 2 mA 以上なければ、ON 時に Franco の補償の抵抗をバイパスする働きが不十分になってしまします。

この回路では MOS FET の場合よりも部品数が増えてしまうこともあり、この回路の実験は行っていません。

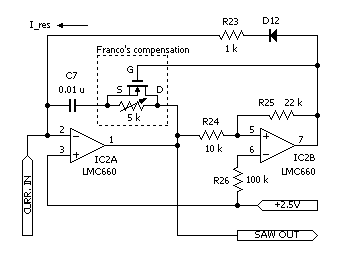

今回、実験を行った N ch MOS FET 使用の回路を下に示します。

は、リセット期間の始めで約 1.4 V、終わりで約 3.6 V ですから、この電圧で十分 ON になる特性の MOS FET が必要です。

また、構造上、ドレイン・ソース間に寄生ダイオードが存在するものが多く、OFF となるべき、非リセット期間で影響を与えないように、ドレイン・ソースの向きは回路図に示すような方向にする必要があります。

FET が ON するリセット期間では、ドレインの電位がソース電位より低くなりますが、ON 抵抗が十分低ければ、電位差はほとんど生じません。

また、パワーMOSFET はゲート容量が数百〜数千 pF と大きく、ドライブしきれないので適しません。

ここでは、手持ちの中から、表面実装型、ソース共通のデュアル MOS FET である、μPA572T (NEC) を使いました。

もちろん、デュアルタイプである必要は全くなく、単に使わない側の FET はゲートもドレインもソースに接続して機能しないようにしています。

一般的なリード線タイプでは、使ってみた経験はありませんが、価格とスペック上から選ぶと 2SK1132 (NEC製、廃品種、サトー電気で単価 32 円) が良さそうです。

MC14577 を使った、小電流領域での波形写真を下に示します。

リセット期間の始めの方で、積分器出力の波形が曲がっているのは、その部分ではゲート電圧が 1.4 V 程度と大きくなく、ON 抵抗が高い状態で、リセット電流による電圧降下が見えているのだと思います。

リセット期間の終わりではゲート電圧は 3.6 V 程度となり、ON 抵抗は低くなって、スパイク状のトランジェントは見えていますが、非リセット期間との電圧レベル差はほとんどありません。

大電流領域での波形写真を下に示します。

リセット期間の始めの落ち込みと、リセット期間の終わりの持ち上がりは Franco の補償の抵抗での電圧降下によるものです。

入力電流と発振周波数をリニア・スケールで示したグラフを、前回のショットキ・ダイオード版と、補償なしのオリジナル回路版での結果と共に示します。

Franco の補償ありの2本のグラフは直線になっており、補償なしのグラフとは明らかに異なっています。

ショットキ・ダイオード版では によるヒステリシス幅の減少により、全体的に発振周波数が上昇していることも分かります。

今回の回路でのセント単位での誤差のグラフを示します。

前回と同様に、オシロスコープによるラフな調整を行ったので、誤差は多めに出ています。

精密に調整すれば、もっと誤差の少ない状態に追い込めると思います。

次回は、CMOS アナログスイッチを使用した回路です。