ATtiny10 用プログラム (14)

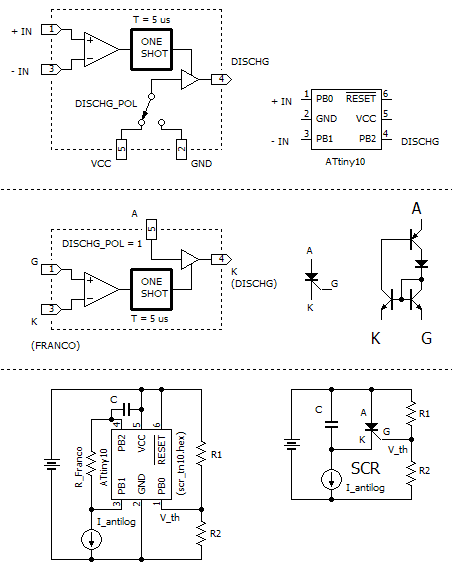

VCO 回路の「コンパレータ + ワンショット」部分を ATtiny10 のプログラムとして実現しました。

(gcc の gas ではなく)AVR ネイティブのアセンブラで書いてあり、そのソースリストは次回に掲載します。

タイマ IC 555 を使ったリセット型 VCO 回路なら 555 の部分、MS-20 などの SCR (サイリスタ) 相当の回路を使ったリセット型 VCO なら SCR 部分、LM331 を使ったリワインド型 VCO なら LM331 の部分に相当します。

ソース・プログラムの設定を変えて再アセンブルすれば、外部 SYNC 出力、あるいは外部 SYNC 入力 (Hard sync) にも対応しますが、それについては次回説明します。

すべてのタイミングは、内部 8 MHz クロックで離散化されますから、原理的にピーク・ツー・ピークで

1 / 8 [MHz] = 125 [ns]

のジッタが除去できずに、常に存在します。

また、当然、電源電圧の最大値は 5 V までとなります。

リセット型 VCO の SCR 回路と対比させたブロック図を下に示します。

コンパレータ部分は、ATtiny10 内蔵のアナログ・コンパレータです。

ワンショット部分はプログラムで実現してあります。

ATtiny10 の出力ポートの ON 抵抗は 30 〜 40 Ω のオーダーなので、この抵抗値で十分に放電できるように、ワンショットのリセット/リワインド・パルス幅は約 5 μs と、少し長めにとってあります。

もちろん、ソース・プログラムの設定を変え、再アセンブルすれば変更できます。

「DISCHG_POL」の設定により、SCR 相当の回路、および PUT 相当の回路にできます。

上の図の中段は、DISCHG_POL = 1 の設定で SCR 相当にした場合の、SCR のアノード (A)、カソード (K)、ゲート (G) 各電極との対応を示しています。

Franco の補償の抵抗を挿入できるように、カソード電極は放電用と、電圧センス用との、2 つの端子に分割してあります。

この分割により、外部リセット素子の利用や、リワインド型の VCO としても使えます。

上の図の下段は、SCR を使用した VCO 回路との対比です。

RFranco = 0 なら SCR 回路と同等になります。

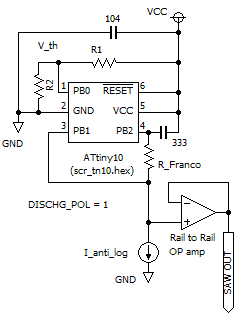

左にリセット型の構成での具体的な回路を示します。

タイミング・コンデンサの値として、0.033 μF (333) を示してありますが、電源電圧 5 V で、リセット・パルス幅 5 μs 程度という条件で、リセット期間内に十分放電し切る容量は、この程度の値になります。

リセットは電源電圧に向かって行われるので、バッファとして使う OP アンプは入出力とも、電源電圧レイルから使用可能な必要があります。

あるいは、OP アンプの電源電圧は高く (たとえば 5 V)、ATtiny10 の部分の電源電圧は低く (たとえば 3.3 V) することにより、電源レイル側の入出力に制限のある OP アンプを使うこともできます。

外部リセット素子を使う場合の回路を左に示します。

PNP タイプのバイポーラ・トランジスタを使う場合の例になっています。

いわゆる「デジタル・トランジスタ」を使っていますが、普通のトランジスタと抵抗でもかまいません。

PB2 (4 番ピン) をリセット用トランジスタのベース・ドライブに使うので、リセット期間の間 GND 側に引っ張る必要があり、DISCHG_POL = 0 の設定でアセンブルしたオブジェクトを書き込んでおきます。

この構成の場合、リセット用トランジスタに大電流を流せば、リセット・パルス幅は 5 μs より短い設定にできます。

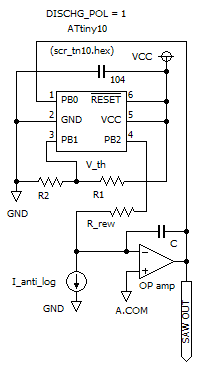

「リセット型」ではなく、「リワインド型」の構成での回路を左に示します。

この場合、OP アンプを (反転型) 積分器として使うので、入出力の電位を OP アンプの都合の良いレベルに合わせて設定することが可能であり、特にレイル・ツー・レイル型の OP アンプを選択する必要はありません。

リセット型と比較すると、スレシホールド電圧と、コンデンサ端の電圧との接続先の端子が逆になっています。

積分器を使っているので、一定のリワインド電流を流すのに、Rrew の抵抗一本で済んでいます。

「DISCHG_POL」の設定は外部リセットを使わない場合のリセット型の場合と同じ「1」になっています。

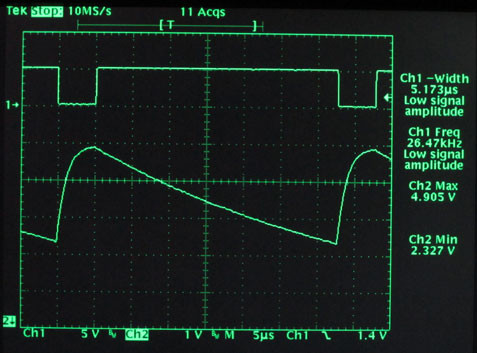

外部リセットを使わない場合のリセット型での波形写真を下に示します。

この写真は、次回説明する外部 SYNC 出力のモードでの波形で、上のトレースが SYNC 出力パルスで、負極性のパルス部分がリセット期間を示しています。

SYNC 出力パルス極性は「SYNC_POL」の設定で変えられます。

上の写真の下側のトレースは OP アンプ出力波形で、0.033 μF (333) のタイミング・コンデンサが、約 5 μs のリセット期間内に、完全には放電しきっていないような波形になっています。

アンチログ回路の定電流出力ではなく、単なる抵抗で「充電」側の電流を決めているので、のこぎり波の斜辺が直線ではなく、曲がっています。

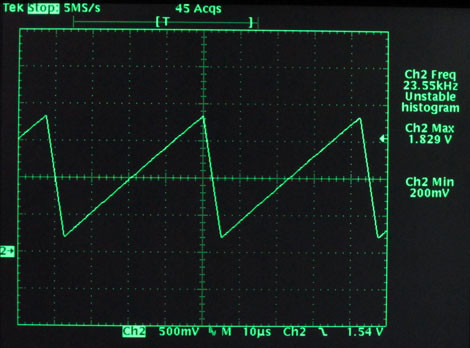

下の写真は、リワインド型の構成での OP アンプ出力波形です。

こちらも、充電電流は抵抗一本で決めていますが、反転型積分器を使っているので、定電流での充電となり、直線となっています。

最後に、ATtiny10 に書き込むべき HEX ファイル「scr_tn10.hex」を示します。

:100000000AC040C02AC03EC03DC03CC03BC025C065 :1000100031C038C037C00FE50DBF00E00EBF11275B :1000200008ED0CBF00E006BF0FE007BB11B913B924 :10003000129AF99AF89AFB9A08D000E601BF7894D0 :1000400001E00ABF88951ABFFBCF0A9A00270A95DC :10005000F1F71A95E1F70A9808950A9A0F930FB7E6 :100060000F930AE00A95F1F70F910FBF0F910A98CD :10007000A89518950F930FB70F93E7DF0F910FBF58 :060080000F911895189580 :00000001FF

ソース上の設定としては、

.set SYNC_MODE = 0 ; no sync OUT / IN .set SYNC_POL = 0 ; negative going pulse .set DISCHG_POL = 1 ; discharge to 'VCC' rail .set DISCHG_CLKS = 41 ; discharge period = 41 clocks

となっており、プログラム・サイズ 134 バイト、SRAM はスタックとしての使用のみです。