PSoC 4200 Prototyping Kit (16)

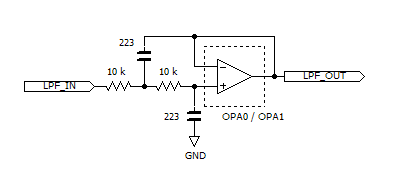

SdmDac16 のテスト・プロジェクトでは、1 ビット DAC 出力に下図のような内蔵 OP アンプを利用した Sallen-Key トポロジの 2 次バタワース LPF (fc = 4.8 kHz) を接続してアナログ電圧を得ています。 (このシリーズの記事の 1 回目に PWM DAC 用に使った LPF と同じです)

上の図は片チャンネル分ですが、実際には OPA0 / OPA1 を使用して同一の回路を 2 組作製し、ステレオ構成としています。

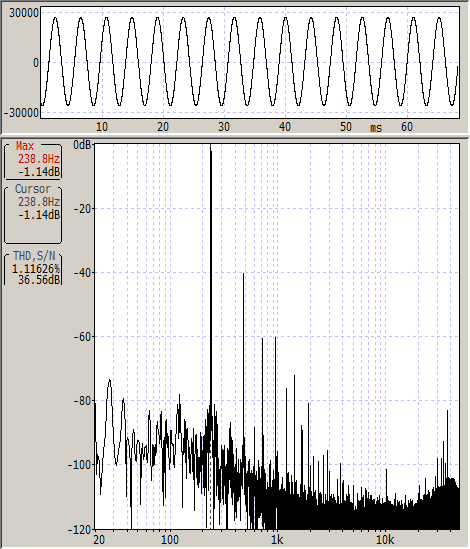

WaveSpectra で出力正弦波信号のスペクトルを観測した結果を下に示します。

2 次高調波の基本波に対する相対レベルは -40 dB 程度で、ひずみ率は 1 % を超えています。

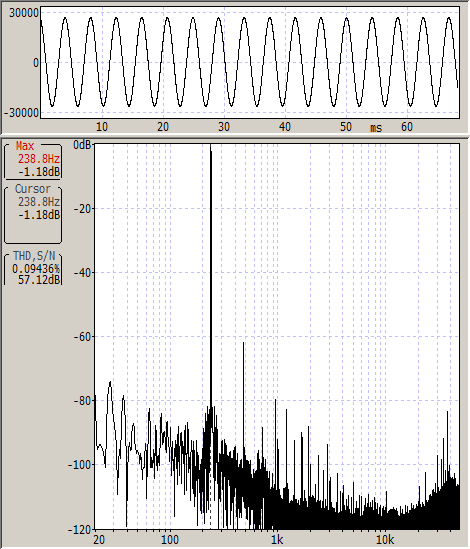

なんとか改善できないかを、いろいろと試したところ、理由は分かりませんが次のような設定で最もひずみ率が低くなりました。

- LRCLK を発生させる TCPWM コンポーネントは 48 MHz クロックで駆動

- SdmDac コンポーネントは 24 MHz クロックで駆動

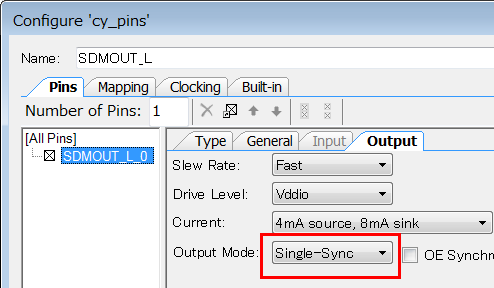

- 出力ピン (SDMOUT_L / SDMOUT_R) は HFCLK (48 MHz) でフリップ・フロップを叩く、「Single-Sync」の設定にする

出力ピンはデフォルトでは「素通し」(Transparent) の設定になっているので、「Single-Sync」の設定に変更するには、下の図のように「Pins」タブの下の「Output」サブタブの画面を開きます。

このような設定をした結果、2 次高調波の相対レベルは -60 dB 以下、ひずみ率は 0.1 % 以下という、まあまあの性能になりました。

外部の OP アンプを使用した場合でも同じような傾向が見られます。

データパス・セルからの出力は、データパス・クロック (24 MHz) で同期が取られているはずなのですが、それを 48 MHz クロックで同期を取り直すと改善するというのは、なぜだか良く分かりません。