PSoC 4200 Prototyping Kit (12)

PSoC4 の内蔵アナログ・ブロックの OP アンプとコンパレータ、内蔵 UDB (Universal Digital Block) 上の PWM コンポーネントを利用して電荷平衡型 VFC (Charge Balancing Voltage to Frequency Converter) を構成し、内蔵 8 ビット電流出力 DAC (IDAC8) の特性を測定してみました。

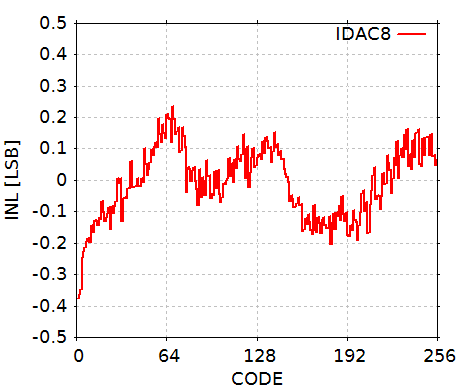

その結果、ゼロ付近の数個のコードを除いて、INL (Integral Non-Linearity: 積分直線性誤差) は ±0.25 LSB 程度で、9 ビット相当の精度があることが分かりました。

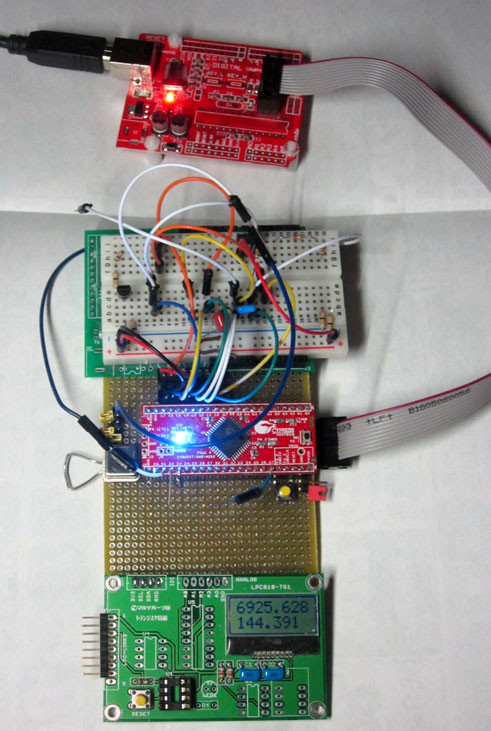

PSoC 4200 Prototyping Kit とその周辺回路を「びんぼうでいいの」のブレッドボード・シールド上に実装するのは手狭になってきたので、PSoC 4200 Prototyping Kit をユニバーサル基板に実装して「びんぼうでいいの」からは独立させることにしました。

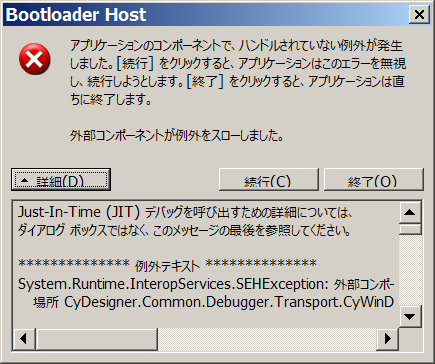

当初は CQ 出版の V850 ボードに実装されている Silicon Labs の CP2104 を利用するつもりで作業を始めたのですが、実際に CP2104 経由で「Bootloader Host」を動作させると下のようなエラー・ダイアログが表示されて、それ以降の書き込み動作などが行えませんでした。

当然、もともとの USB-シリアル変換チップである CY7C65211 では問題ありません。

一方、Nucleo F401RE の CMS-DAP 部分のおまけの USB-シリアル変換機能や、LPC11U35 上に実現した USB-シリアル変換機能では「Bootloader Host」上で COM ポートとして認識されず、それ以降の操作が行えませんでした。

もちろん、いずれの場合も一般のターミナル・ソフトでは COM ポートとして問題なく使えています。

シリアル経由での書き込みを行うための現実的な選択肢として、Prototyping Kit のもともとの CY7C65211 チップを使うか、これまでうまく使えていた「びんぼうでいいの」の CH340T チップを使うかを迫られたわけですが、作業の手間を考えて、「びんぼうでいいの」を使うことにしました。

まだ ATmega などの部品を実装していない「素」の状態の「びんぼうでいいの」に USB (標準) B レセプタクルと 10 p ヘッダ・ピンを実装し、Prototyping Kit 側のユニバーサル基板とはフラット・ケーブルで接続しています。

10 p のヘッダは、USBasp と接続するためのもので、UART 入出力とは接続されていませんが、他の部品は未実装なので、本来は SPI の MOSI/MISO 用のピンなどを利用して UART 入出力と +3.3V 電源を接続しています。

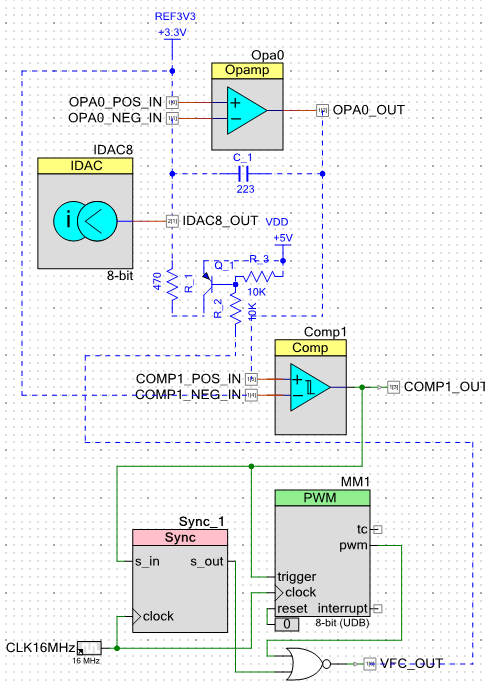

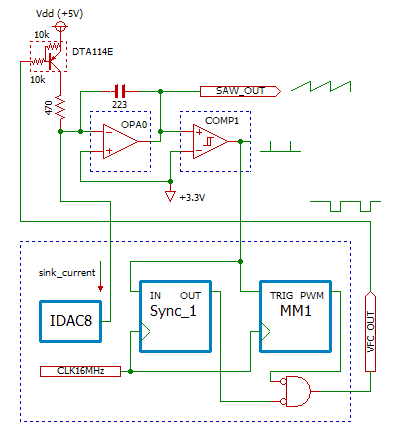

電荷平衡型 VFC 部分のトップ・レベルのデザインを下に示します

「電荷平衡型 VFC」は、これまで「リワインド型 VCO」と呼んできたものと同じです。

今回の応用では、のこぎり波出力は利用せず、パルス出力の周波数を測定することが目的なので、それにふさわしい呼び方にしました。

「VFC_OUT」端子をタイマのキャプチャ入力端子に接続して周波数を測定します。

青色の破線で描かれている部分がが off-chip (チップ外) の外部回路です。

外部回路としては単純な配線を除けば、抵抗 1 個、コンデンサ 1 個とデジタル・トランジスタ 1 個です。

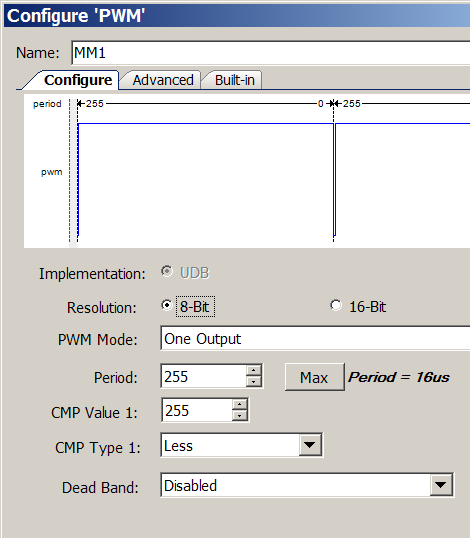

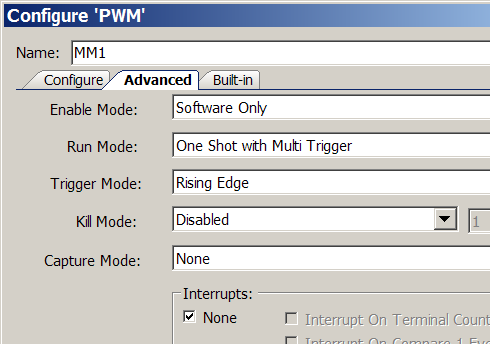

PWM コンポーネント (インスタンス名: MM1) の設定画面を下に示します。

PSoc Creator の図では回路が分かりにくいので書き直したものを下に示します。

青色の破線で囲ってある部分が PSoC4 のチップ内の部分です。

電荷を注入する時間幅 (リワインド・パルス幅) を決めているのが UDB 上の PWM コンポーネントです。 「ハードマクロ」の TCPWM コンポーネントでは PWM モードで「ワンショット」(モノマルチ) 動作ができないので UDB のコンポーネントを使用しています。

16 ビット PWM にすると UDB をふたつ消費してしまうので、8 ビット PWM として UDB の消費を 1 個におさえ、クロックを 16 MHz と遅くしてリワインド・パルス幅を約 16 μs としています。

初期状態などで、のこぎり波出力が Vdd に貼り付いた状態からでも発振を開始できるように、コンパレータ出力のエッジでモノマルチにトリガを掛けるたけでなく、コンパレータ出力の「レベル」もリワインド・パルスに加えています。

モノマルチとして使っている PWM コンポーネント内部でトリガ入力はクロックに同期化されているので、出力に反映されるまでのディレイが発生します。

SYNC コンポーネントを利用して、「レベル出力」側のディレイを調節し、不正な「ハザード」が出ないようにしています。

VFC 回路 (リワインド型 VCO) としては、NPN トランジスタによるシンク電流型アンチログ回路との組み合わせを考えているので、電流出力 DAC はシンク電流モードで動作させています。

8 ビット電流出力 DAC (シンク電流モード) の特性の測定結果のグラフを下に示します。

ゼロ付近の数個のデータを除いたデータから回帰直線を求め、それを「理想変換特性」と見なして、そこからの誤差を求めて積分直線性誤差 (INL) として表示したものです。

ゼロ付近を除けば、誤差は ±0.25 LSB の範囲におさまっていますから、実質的には 9 ビット相当の精度があると言えます。