FPGA 版 FM 音源 (51) -- YMF297 (OPN3/OPL3) 測定 (16) -- EG クロック・プリスケーラ (3)

標準ロジック・ファミリではバイナリ・レート・マルチプライア IC として、TTL の 74 シリーズでは 7497 (6 ビット)、メタルゲート CMOS の 4000B シリーズでは 4089B (4 ビット) などがあります。

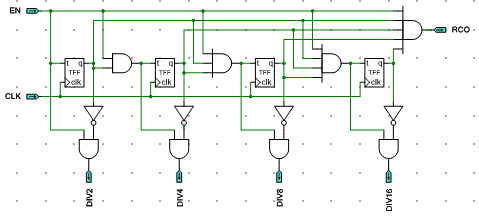

それらの機能を一部簡略化し、ほぼ同等の PSoC コンポーネントとして実現した回路を下に示します。 (図をクリックすると拡大します)

図の上半分は「普通」のバイナリ 4 ビット同期アップ・カウンタです。

RCO (Ripple Carry Output) を次段の EN (Enable) 端子と接続することによりビット数の拡張が行なえます。 TTL の 74169 などの 4 ビット・バイナリ・カウンタと同様です。

PSoC5LP UDB のマクロセルの本来の機能としては、非同期式リセット入力を持つ T-FF を実現できますが、回路図のコンポーネントとしてはリセットなしの T-FF しか用意されていないので、上の回路ではリセット機能はありません。 (回路図ではなく verilog で記述すれば非同期リセットは実現可能)

図の下半分がレート・マルチプライアとしての出力を作成している部分です。

「DIV2」出力からはクロックの 1/2 の周波数のパルスが、「DIV4」出力からはクロックの 1/4 の周波数のパルスが、「DIV8」出力からはクロックの 1/8 の周波数のパルスが、「DIV16」出力からはクロックの 1/16 の周波数のパルスが、それぞれ互いに重なり合わないタイミングで出力されます。

7497 や 4089B とは違って、クロック自体の「間引き」は行なわず、「クロック・イネーブル」信号を作り出すのが目的なので、出力に対してクロックでのゲーティングは行なっていません。

アップ・カウンタ部分の FF トグルを制御する信号を利用して回路を簡略化しています。

7497 では AND ゲート 1 段でレート・マルチプライア出力を作成していますが、これは各入力経路の遅延量のばらつきを原因とする「ハザード」を防止するために遅延量をゲート 1 段分に揃えているものと思われます。

EG クロック・プリスケーラとしては、クロック周波数は高々 50 kHz のオーダーですし、「クロック」そのものとして使用するわけではなく「クロック・イネーブル」信号として利用するのでダイナミック・ハザードは問題になりません。

PSoC Creator で実際に UDB 上にインプリメントされる場合には、PLD 入力数が 12 であるのに対応して、12 ビット目の出力までは上の回路図通りではなく、 7497 の回路のように PLD 1 段で実現されるようです。 13 ビット目、14 ビット目のデコーダは 12 入力の PLD ひとつにはおさまらないので、分割されて PLD 2 個に割り当てられます。

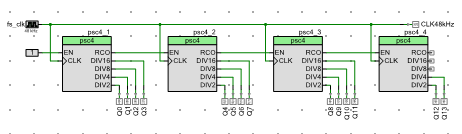

上のコンポーネント (psc4) を利用して、14 ビット・プリスケーラを実現した回路を下に示します。 (図をクリックすると拡大します)

UDB リソースの使用状況を .rpt ファイルから抜粋して示します。

---------------------------------------------------------

Technology mapping summary

---------------------------------------------------------

Resource Type : Used : Free : Max : % Used

=========================================================

UDB Macrocells : 30 : 162 : 192 : 15.63%

UDB Unique Pterms : 27 : 357 : 384 : 7.03%

UDB Total Pterms : 29 : : :

. . . . . <中略> . . . . .

---------------------------------------------------------

PLD Packing Summary

---------------------------------------------------------

Resource Type : Used : Free : Max : % Used

====================================================

PLDs : 9 : 39 : 48 : 18.75%

---------------------------------------------------------

Final Placement Summary

---------------------------------------------------------

Resource Type : Count : Avg Inputs : Avg Outputs

========================================================

UDB : 6 : 10.17 : 5.00マクロセル を 30 個、PLD を 9 個、UDB を 6 個使用しています。