PSoC5LP Prototyping Kit (33) --- UDB routed clock (2)

PSoC では、低スキューで各ブロックにクロックを分配できる配線網が専用に用意されており、そのクロック専用線を使うクロックを「グローバル・クロック」と呼んでいます。

ただし、その数には限りがあって、PSoC5LP ではクロック分周比を任意に選べるディジタル・クロックは 8 本しかありません。 (アナログ用クロックは別に 4 本)

グローバル・クロック以外のクロックは「routed clock」と呼ばれています。 「routed clock」は「PSoC システムリファレンスガイド」の日本語版では「ルートクロック」と訳されているので、ここではそれに従うことにします。

ルートクロックは、クロック専用ではない普通のディジタル信号用の配線を使って分配されるので、分配先相互のタイミングのズレにより動作が不確実になる可能性があります。

確実な動作のためには、低スキューのグローバル・クロックに同期させるメカニズムが必要になります。

PSoC では、UDB (Universal Digital Block) にクロック同期化のための回路が備えられていて、PSoC Creator がルートクロックの使用を検出すると、ルートクロックを作り出している回路で使用されているグローバル・クロックを探し当て、自動的にクロック同期化ハードウェアを利用するような設定を行います。

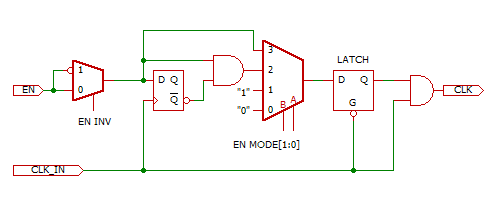

このクロック・コントロール回路については「PSoC5LP Architecture TRM」の「21.3.4.1 Clock Control」の項に回路図が示されていますが、その一部を省略し簡略化したものを下に示します。

クロック入力をイネーブル信号でゲートして出力するものです。

2 入力の MUX (マルチプレクサ) と 4 入力の MUX の設定で多様なモードに対応します。

一番多く使われるのが、4 入力 MUX の入力 1 に接続されているロジック「1」が選択される場合で、クロックは、そのまま連続で素通しの状態になります。 (リポート・ファイルで「Clock Enable: True」と表示される状態)

ルートクロックの同期化では、もとになるグローバル・クロックをクロック入力に、ルートクロックをイネーブル入力に接続します。

2 入力 MUX は入力 0 が選ばれてイネーブル信号の反転なし、4 入力 MUX は入力 2 が選ばれてイネーブル信号の立ち上がりエッジが検出される状態になります。 (リポート・ファイルで「Clock Enable: PosEdge(.)」と表示される状態)

2 入力 MUX の入力 1 が選ばれるとイネーブル信号が反転されて、イネーブル信号の立ち下がりエッジを検出するモードになります。

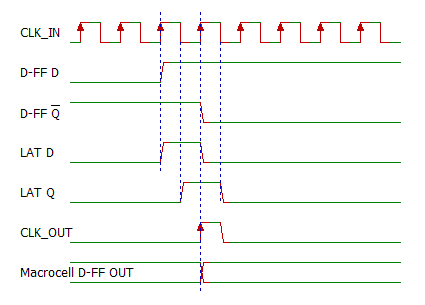

立ち上がりエッジを検出するモードでのタイミング・チャートを示します・

イネーブル信号を反転していないので、D-FF の D 入力はイネーブル信号そのものになっています。

イネーブル信号が立ち上がった後、最初のグローバル・クロックの立ち上がりから 1 パルスだけクロックが出力されます。

そのクロックが入力されているマクロセルの D-FF 出力も、イネーブル信号の立ち上がりの後の最初のグローバル・クロックの立ち上がりで変化します。

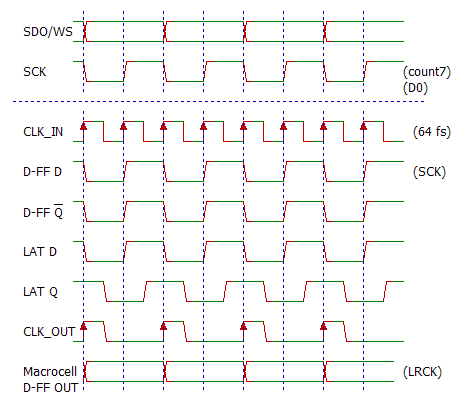

I2S WS → LRCK 変換回路のグローバル・クロック fs_x64、ルートクロック SCK の場合に当てはめたタイミング・チャートを示します。

水平の破線の上側は I2S コンポーネントの信号を示しています。

I2S コンポーネントの内部回路は fs_x64 の立ち上がりエッジで信号が変化しています。

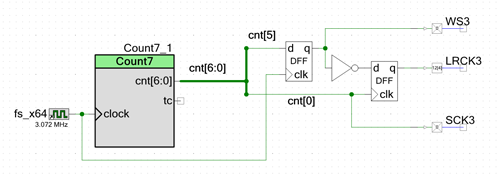

タイミング信号は、ステータス/コントロール・ブロック中の 7 ビット・ダウンカウンタ「count7」を利用して発生しており、count7 の最下位ビット count_0 を SCK として出力しています。

データパス・セル内部では SDO 信号が SCK の立ち上がりの位置に同期して変化していますが、SDO/WS については fs_x64 でクロックされる D-FF 1 段を介して出力されており、変化するタイミングは SCK の立下り位置となっています。

SCK の立ち上がりを検出して、実際にクロック・パルスが出力されるのは次の fs_x64 クロックの立ち上がりの位置、つまり、SCK で見れば立ち下がりの位置になっています。

これが「論理的には正しくない」回路が実際には正しい出力となる原因です。

エッジ検出回路の 1 クロック・ディレイが、2 分周されたクロックに対しては半周期の遅れとなり、立ち上がり/立ち下がりが入れ替わることになります。

このクロック・コントロール回路は UDB ひとつに付き 4 回路用意されていて、

- PLD 2 系統

- データパス・セル 1 個

- ステータス/コントロール・ブロック 1 個

の 4 つそれぞれのクロックとして使われます。

ひとつの PLD には 4 つのマクロセルが属し、4 個の D-FF が同じクロックで駆動されます。

D-FF 1 個の回路がルートクロックとして扱われて、クロック・コントロール回路が設定されると、同じ PLD に属する残りの 3 個の D-FF も同じクロックで動作することになります。

そのクロックで動作する用途がなければ、その 3 個は、単に利用されない D-FF となってしまいます。

前回、オーソドックスな方法として示した D-FF 2 個による方法は、クロックとしてグローバル・クロックである fs_x64 を入力しているので、残り 2 個の D-FF も活用できる可能性が残っています。

I2S コンポーネントの WS 回りの回路を、もう少し踏み込んだモデルで記述すると下のようになります。

上の回路を含めてビルドした結果のリポート・ファイル中の routed clock 検出結果を示します。

<CYPRESSTAG name="UDB Routed Clock Assignment"> Routed Clock: \I2S0:BitCounter\:count7cell.count_0 Effective Clock: fs_x64 Enable Signal: \I2S0:BitCounter\:count7cell.count_0 Routed Clock: \Count7_1:Counter7\:count7cell.count_0 Effective Clock: fs_x64 Enable Signal: \Count7_1:Counter7\:count7cell.count_0 </CYPRESSTAG>

I2S コンポーネントと、モデル回路で同様に count7 の count_0 がルートクロックとして扱われているのが分かります。