FPGA 版 FM 音源 (58) -- FPGA 版 EG (2)

もうずいぶんの間、YMF297 の測定の話からは離れており、この先しばらくは触れることもないので、今回から「YMF297 測定」をタイトルから外しました。

前回の回路では、EG モジュール内部の信号も引出していたのでピン数が 75 本と多く、100 ピンパッケージでユーザ I/O ピン数が 65 本しか取れない EP1C3T100C8 にはフィッティングできません。

また、クロック関係はモジュール外部で生成されることを仮定しているので、EG モジュールだけを実現したのでは外部回路の負担が大きくなります。

そこで、クロック発生回路や、対数 — リニア変換回路、SPDIF 送信回路、I2S DAC 送信回路、シグマ・デルタ DAC なども含めて実現しました。

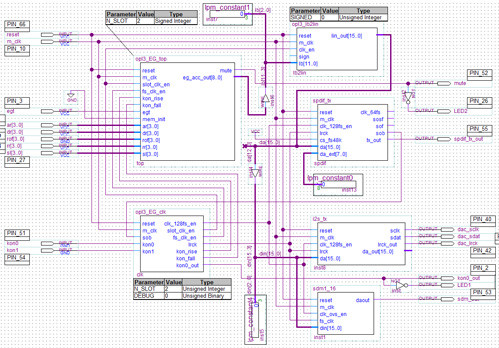

そのトップレベルの回路図を下に示します。 (図をクリックすると拡大します。)

これ全体で、スロット数 N_SLOT = 2 の場合の LE (ロジック・エレメント) 使用量は 339 です。 (N_SLOT = 1 の場合は 331 LE)

左上の「opl3_EG_top」がピン数を減らした EG モジュール本体です。

その他のモジュールを単独でコンパイルした場合の LE 使用量の表を下に示します。

| モジュール名 | LE 使用量 | 説明 |

|---|---|---|

| spdif_tx | 66 | spdif 送信部 |

| i2s_tx | 36 | I2S (標準フォーマットのみ) 送信部 |

| sdm1_16 | 35 | 16 ビット入力 1 次シグマ・デルタ DAC |

| opl3_lb2lin | 46 | 対数 — リニア変換(M4K メモリ使用) |

| opl3_EG_clk | 30 | クロック生成 / KON チャタリング除去 |

「メイン・クロック」(m_clk) として 18.432 MHz のクリスタル・オシレータを使用し、それを「opl3_EG_clk」モジュールで 3 分周して SPDIF 送信モジュールで必要な 128 fs = 6.144 MHz を得ています。

それに加え、「opl3_EG_clk」モジュールでは「スロット・クロック・イネーブル」信号、「fs クロック・イネーブル」信号、ステレオ・シリアル DAC 用の LRCK などを生成しています。

さらに、KON (Key ON) 入力のチャタリング除去も行なっています。

基板の写真を下に示します。

SPDIF および I2S ステレオ・オーディオ DAC により 2 系統の出力が実現できるので、スロット数 N_SLOT = 2 として、2 系統のエンベロープを発生させています。

しかし、実際に 2 系統の入力を実現するとスイッチへの配線が面倒になるので、AR / DR / SL / RR / Rof / EGT のパラメタについては 1 系統のディップ・スイッチを設けるだけとし、2 系統のエンベロープで共通に利用しています。

KON については 2 系統設けて、キーオン/キーオフ・タイミングのみ 2 系統独立としています。

SPDIF でステレオ・チャプチャした結果を波形編集ソフトで表示したものを下に示します。

上側が L ch で、マニュアルで KON0 のタクト・スイッチを操作したもの、下側が R ch で、555 で約 1.4 s 周期のパルスを発生させて KON1 に入力したものです。

EG パラメタは共通なのでエンベロープの形状は同一ですが、キーオン/キーオフのタイミングについては独立で互いに干渉は見られません。