FPGA 版 FM 音源 (77) -- TX7 (OPS) 測定 (4)

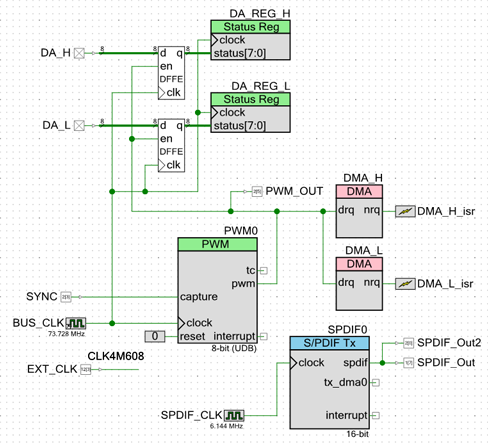

TX7 DAC データ・キャプチャのための内蔵ペリフェラルおよび「外部ハードウェア相当部分」の回路図を下に示します。 (図をクリックすると拡大します)

外部から「EXT_CLK」端子に入力された 4.608 MHz を PLL で 16 倍して 73.728 MHz を作り出し、システム・クロック (BUS_CLK) として CPU および内蔵ペリフェラルや UDB (Universal Digital Block) に供給しています。

UDB による SPDIF 送信モジュールには BUS_CLK の 73.728 MHz を 12 分周した 6.144 MHz クロックを供給しています。

上の回路は次の 3 つの部分から構成されています。

- PWM モジュールを使った DMA リクエスト・タイミング発生回路

- 16 ビット・パラレル・データ・ラッチ回路および DMA モジュール

- SPDIF 送信モジュール

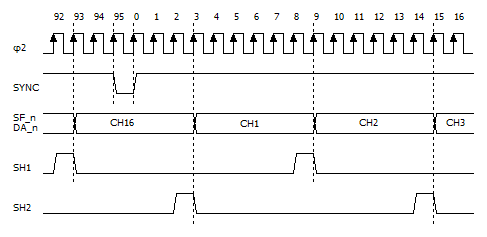

TX7 のタイミング・ダイアグラムを再掲すると、

サンプル/ホールド・タイミングである SH1 / SH2 を、DAC データのキャプチャ・タイミングとして使用することはできますが、SH1/SH2 の立ち上がりのタイミングから 4.608 MHz クロック 1 個分しか当該データは有効ではなく、「タイミング」としては少し遅すぎます。

そのため、キャプチャ・タイミングは BUS_CLK の 73.728 MHz をカウンタで 96 個分数えて 768 kHz レートのタイミング信号を「自前」で作り出しています。

カウンタ自体は「フリーラン」で動かすので、位相を合わせて「同期」を取る目的で OPS の SYNC 信号を PWM モジュールのキャプチャ入力に接続しています。

プログラムのメインループの前に、SYNC 信号のキャプチャを行い、その「位置」がカウンタの 96 カウント・ループのどこに相当しているかを判定しています。

DMA リクエスト信号として使う PWM 出力の位置は SYNC 信号の立ち下がりエッジ (前縁) に近い位置に設定しています。

この処理は一度だけ行い、その後は再度同期を取ることはせず、フリーランで動作させています。

PWM 信号の比較方法は「一致」を選択していて、PWM デューティー値と一致するカウント値の時点で 1 クロック幅の信号が出力されます。

この PWM 信号は DMA データ・リクエスト信号として使われるほかに、16 ビット・パラレル・データを D-FF でラッチするタイミングとしても使われています。

一般のマイコンであれば、この D-FF は外部回路として設けなければなりませんが、PSoC5LP では UDB を利用して「内部」で済ますことができます。

32 ビット Cortex-M3 プロセッサを内蔵している PSoC5LP ですが、UDB 等の周辺回路は 8 ビット・プロセッサ 8051 を内蔵している PSoC3 と共通化されているので、16 ビット幅の IO ポートとか、16 ビット幅のステータス・レジスタとかは用意されていません。

そのため、16 ビット幅のデータを DMA でキャプチャするために、上位 8 ビット用と、下位 8 ビット用との 2 つの DMA チャネルを用意して、2 回の DMA 転送で 16 ビット分のデータをキャプチャしています。

UDB による SPDIF モジュールでは、チャネル・ステータス送信のためにデフォルトで 2 つの DMA が使用されており、これ以上 DMA を「混雑」させないために、SPDIF モジュールへのオーディオ・データの書き込みは DMA や割り込みを使わず、メイン・ループの中でのソフトウェア・ポーリングによって実現しています。