FPGA 版 FM 音源 (76) -- TX7 (OPS) 測定 (3)

4 年前の記事のタイミング・チャートを再掲します。

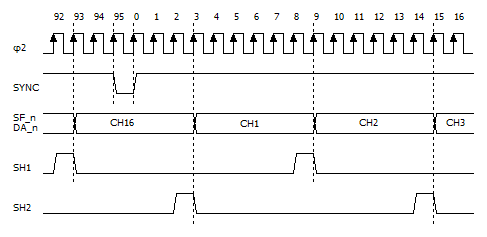

オリジナルの回路では、9.4265 MHz の水晶振動子による源発振を 2 分周して 4.71325 MHz の 2 相ノン・オーバーラップ・クロック φ1、φ2 を作り出し、YM2128 (OPS) および YM2129 (EGS) に供給しています。

OPS と EGS との同期を取るために、サンプリング周期に等しいインターバルで「SYNC」信号が出力されており、その周波数は 4.71325 [MHz] / 96 = 49.09635 [kHz] となっています。

48 kHz サンプリングの SPDIF にデータを乗せるため、源発振の水晶振動子を 9.216 MHz のものに換装しており、以降の各種周波数の記述は、この源発振周波数を基準として記述します。

OPS からのサウンド出力は、仮数部 12 ビット、指数部 2 ビット相当の浮動小数点相当のフォーマットで出力されてきます。

指数部については「デコード」された形で出力されており、SF0 〜 SF3 の 4 本の信号で仮数部を左シフトすべき量 3/2/1/0 ビットを表わしています。

データをキャプチャするには、仮数部 12 本および指数部相当の SF0 〜 SF3 が 4 本の、合計 16 ビット・パラレルのデータを扱う必要があります。

SF0 〜 SF3 は、常にどれか 1 本だけが「1」となり、残りの 3 本は「0」となるので、それを利用すると 4 本中 3 本のみの接続で済ますことができます。

たとえば、SF1 〜 SF3 の 3 本だけを読み込む場合、読み込んだ 3 ビット全部が「0」であることを検出すれば、接続していないビットの SF0 が「1」であることが分かります。

OR ゲート 2 個で SF0 〜 SF3 を 2 進数にエンコードすれば、ビット数は 14 本に減ります。 (「1」になるビットはひとつに限られるので、プライオリティ・エンコーダは必要ない)

サンプリング周波数 48 kHz で 16 音分のデータが出力されるので、パラレル・データの出力レートは 16 × 48 [kHz] = 768 [kHz] となります。

したがって、OPS からの DA 出力データを (16 音分) キャプチャするためには、

- 5 V ロジック・レベルの

- 14 〜 16 ビット・パラレル・データを

- 768 kHz レートで取り込む

必要があります。

まず、「5 V ロジック・レベル」については、

という解決策が考えられます。

一般的に、高クロック、高機能のマイコンは 3.3 V 電源のものが多く、5 V 電源のものは多くありません。

3.3 V マイコンの 5 V トレラント入力を利用するにしても、14 〜 16 ビットが必要となると、ピン数の多いデバイスが必要になってきます。

また、レベル・コンバータを使えば選択可能なマイコンの範囲が広がりますが、OPS → マイコン間の配線の数が「直結」であれば 14 〜 16 本で済むのに、レベル変換 IC を噛ませることにより、倍の 28 〜 32 本になってしまいます。 したがって、これはあまりやりたくありません。

次に、768 kHz というレートですが、φ2 の 4.608 MHz を 8 倍した36.864 MHz を CPU クロックとして使用する場合、1 音あたり 48 クロックしか利用できないことになります。

Cortex-M0 の場合、割り込み応答のレイテンシが 16 クロック程度なので、あまり余裕がありません。 ソフトウェア・ループでポーリングして同期を取る方法もかなり苦しいです。

ここはどうしても DMA が欲しくなります。

一方、 SPDIF 出力側については、

という案が考えられます。

いずれにせよ、SPDIF 用に 128 fs = 6.144 MHz あるいは 192 fs = 9.216 MHz などのシステム・クロックが必要であり、オリジナルのボード上の φ2 から作り出すにはクロック回路に PLL を内蔵しているマイコンが必要になります。

そうでないと、外部で発生させたシステム・クロックを新たな配線によりボードまで引っ張ってくる必要があります。

「ソフト SPDIF」については 16 ビット長以上の SPI モジュールと、DMA の機能が必須になります。

そういうわけで、

- 配線が楽な 5 V 電源のマイコンには低クロック、低機能のものが多く、SPDIF 送信チップとの 2 チップ構成のキャプチャ側チップとしても力不足

という「二律背反」により、なかなか進みませんでした。

3.3 V 電源のマイコンとしては、PIC32MX120F032B が DMA, PLL 内蔵で価格も安く、ソフト SPDIF も実装ずみで好都合なのですが、やはり配線が面倒ということで実際に手を動かすところまでは至りませんでした。

今回は、重い腰を上げて、希少な 5 V 電源の高機能マイコンの PSoC5LP を使って実現しました。