FPGA 版 FM 音源 (36) -- YMF297 (OPN3/OPL3) 測定 (1)

今回は、「FM音源ガチャ」で入手した YMF297 についての話題です。

このチップは、

- YM2203(OPN),YM2608(OPNA),YMF288(OPN3) などの「OPN」系のモードと、

- YMF262(OPL3),YMF289(OPL3-L) などの「OPL3」系のモードとの、

どちらかに切り替えて動作させることができます。

このチップは PC-9800 シリーズの C バス用音源ボード PC-9801-118 (通称 118 音源ボード) に採用されており、その点ではメジャーなチップなのですが、ネット上ではデータシートやアプリケーション・マニュアルを見つけることができませんでした。

私は PC-9800 系の PC には縁がなく、当然 118 ボードの現物を持っているはずもなく、YMF297 チップのピン接続や、何 MHz のクロックが必要なのかさえも分からず、使用するのは無理なのではないかと諦めかけていました。

しかし、キーワード「S98プレイヤー」でググって見つかる web サイトに YMF297 を使用した回路図があり、ピン接続を知ることができました。

このサイトでは、S98/VGM 形式のファイルを音源チップで演奏するための、

- PC 上のアプリケーション・プログラムのソース

- PC と USB 接続するためのハードウェア (EZ-USB, PIC32 など) の回路図およびファームウェア

- 音源チップ・ボードの回路図および基板の写真

が公開されています。

このハンドル名も不明な作者の方は、どういう立場の方か分かりませんが、20 種類くらいの FM 音源チップについて回路を作成されており、その中に YMF297 の回路図もあります。

その回路図を元にしてピン接続を示すと次のようになります。

また、マスタークロックの周波数は fs=44.1 kHz の 384 倍の 16.9344 MHz であることが回路図から読み取れました。

そのほか、接続する DAC は専用ではなく、一般的な 2 の補数 16 ビット・データ右詰め形式の入力フォーマットの DAC を使うようです。

ここで疑問なのが、同じ名前の IC# (Initial Clear input) 信号が 8 番ピンと 21 番ピンの両方に割り付けられていることです。

web の回路図では、両方のピンに同じリセット信号が入力されています。

また、32 番ピンの N/L# 信号は、「H」レベルで OPN モード選択、「L」レベルで OPL3 モード選択のように解釈できますが、実際に切り換えて IC# ピンにリセットをかけても OPN モードのままで切り替わらないように見えました。 レジスタに書き込んでソフトウェア的に設定するのかも知れません。

OPL3 モードに切り替われば fs=44.1 kHz に相当する DAC タイミング出力となると思われますが、OPN モードと思われる fs=55.52 kHz の DAC タイミングのままで切り替わらないようです。

もう少し詳しくいうと、OPN モードでビット・クロック (BCO) の周波数は、

16.9344 MHz / 5 = 3.38688 MHz

LR クロック (LRO) の周波数は

16.9344 MHz / (5 × 61) = 55.523 kHz

となっています。

1 オーディオ・フレーム当たりのビット・クロック数が偶数ではなく、 61 という奇数 (しかも素数) になっていますが、これは、YM2608/YMF288 では標準のマスタークロック周波数が 8 MHz で、サンプリング周波数が

8 MHz / 144 = 55.556 kHz

となるので、なるべくそれに近い値を得るためだと思われます。

1 フレーム当たりのビット・クロック数が 60 や 62 だと、サンプリング周波数が

3.38688 MHz / 60 = 56.448 kHz

3.38588 MHz / 62 = 54.627 kHz

となり、誤差が大きくなります。

ビット・クロック数が奇数ということは、LR クロックのデューティーが正確に 50 % でなくなるということで、DAC に ROHM の BU9480 を使う場合に問題となります。

BU9480 では、隣接サンプル間の算術平均を取って出力することにより簡易的な 2 倍オーバーサンプリングを実現しているので、LR クロックのデューティーが 50 % でなくなると歪みが増加する結果となります。

サンプリング周波数 48 kHz の S/PDIF に乗せるためのマスタークロック周波数を逆算すると、

48 kHz × 5 × 61 = 14.64 MHz

となります。

特注ではない、出来合いの水晶振動子の周波数に「61」の因子が含まれていることは期待できませんから、「61」という因子は PLL 回路で周波数を 61 倍することで実現する必要があります。

よく使っているマイコンで、61 倍 (以上) が可能な PLL を持つものは、Nuvoton の NUC120 と、STMicro の STM32F4xx シリーズだけです。

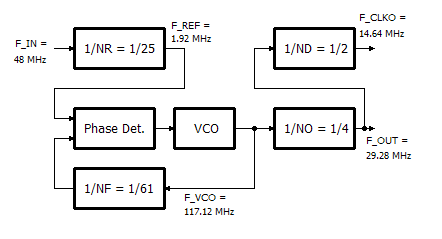

NUC120 で 14.64 MHz を得る構成を下に示します。

外部クロック入力は、USB 用の周波数の 48 MHz のクリスタル・オシレータを使います。

ただし、この構成では、S/PDIF トランスミッタ用のオーバーサンプリング・クロックは発生できません。

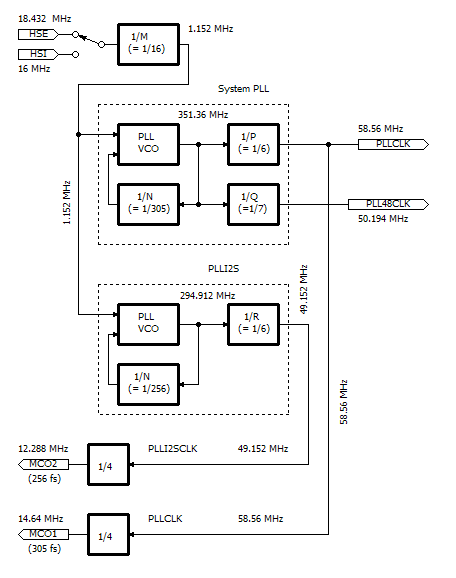

STM32F4-Discovery あるいは Nucleo F401RE の STM32F4xx マイコンでは、384 fs の 18.432 MHz の水晶振動子を使って、下のように 305 fs の 14.64 MHz と、256 fs の 12.288 MHz を同時に得ることができます。

ただし、USB 用のクロックは 48 MHz を実現できないので USB モジュールは使用不可です。

Nucleo F401RE 上にこの構成を実現して、14.64 MHz クロックを YMF297 に供給し、OPN モードでサンプリング周波数が 48 kHz となることを確認しました。