OTA/VCA/PGA を使用した 2 次特性 VCF (12)

実際に NJW1159 を使った状態変数型フィルタを作成し発振させて、その周波数を測ってみました。

回路規模が大きくなるので、Arduino 用の小さなブレッド・ボード・シールドではなく、大きいブレッド・ボード上に回路を組み、コントロール用のマイコンとしては PSoC5LP Prototyping Kit を使用しました。

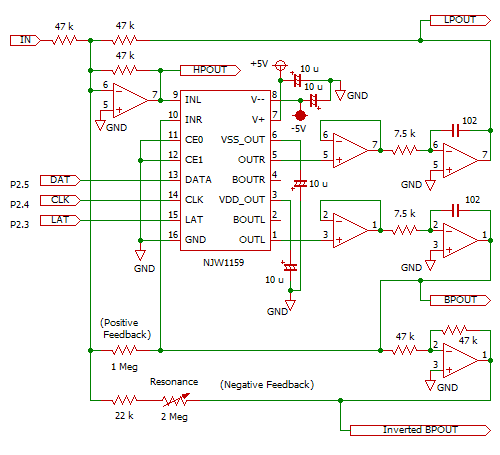

フィルタ部分の回路図を下に示します。

ボルテージ・フォロアと積分器の OP アンプとしては TI 製の TLE2082 を、入力部の反転型加算器とバンドパス出力の反転出力には JRC 製の NJM2082 を使用しています。 NJW1159 内蔵のボルテージ・フォロアは使用していません。

スルーレート、ゲイン・バンド幅などの特性は TLE2082 の方が良いのですが、手持ちが 2 個しかなかったので、不足分の 1 個は NJM2082 を使用しています。

単にバンドパス出力からの負帰還パスをオープンにするだけではゲインの小さい、つまり低周波数の領域で発振しなかったので、1 MΩ の抵抗で「正帰還」のパスを設けています。

特に振幅制限のための回路を設けなくても、各 OP アンプ出力の自然なクリップだけで減衰量 0 dB 〜 59 dB の範囲で発振しました。

周波数の測定は、PSoC4 の場合と同様のレシプロカル周波数カウンタのハードウェア/ソフトウェアを PSoC5LP 上に実現して行いました。

波形整形およびレシプロカル周波数カウンタ部分の回路を示します。 (画像をクリックすると拡大します)

16 ビット・カウンタを 2 個使った PSoC4 の場合とは違って、UDB (Universal Digital Block) を使って素直に 32 ビット・カウンタ 1 個を作成しています。 データパス・セル 4 個 (UDB 4 個分) を消費します。

PSoC5LP 内蔵コンパレータでは約 10 mV のヒステリシスを設定することができますが、ヒステリシスの幅が小さすぎて低い周波数のサイン波入力ではエッジ部分でバタついたので、外部回路で約 0.11 V のヒステリシスを設けるようにしました。

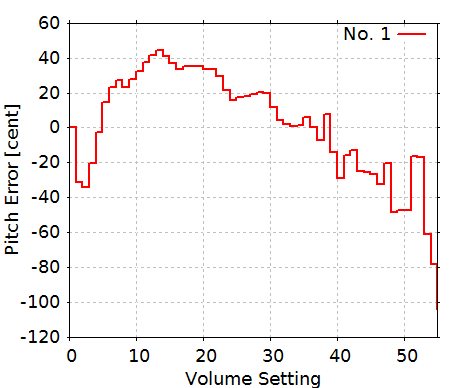

個体番号 1 の NJW1159 チップに対する発振周波数の測定結果を下に示します。

減衰量 0 dB の場合に誤差なしと見なし、また、公称 1 dB ステップ = 1 全音 (2 半音、200 セント) と見なして、期待される周波数からの誤差をセント単位で表しています。 (1 半音 = 100 セント、1 オクターブ = 1200 セント)

NJW1159 への設定値 56 以降のグラフは表示していませんが、急激に誤差が大きくなって、設定値 59 で -400 セント程度になります。