FPGA 版 FM 音源 (53) -- YMF297 (OPN3/OPL3) 測定 (18) -- EG クロック・プリスケーラ (5)

PSoC5LP UDB 上にローレート専用の EG アキュムレータ部分も実装して、連続してアタックとディケイを交互に繰り返す回路を作りました。

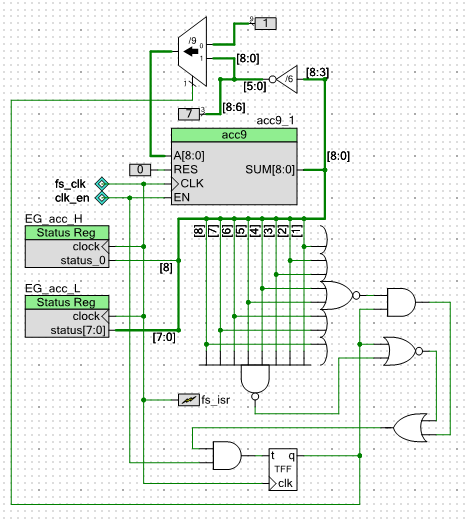

回路図を下に示します。 (図をクリックすると拡大します)

EG クロック・プリスケーラ部は 2016 年 12 月 2 日付けの記事 (→こちら) と同じものを別のシートに記述してあります。

また、別のシートに SPDIF_Tx コンポーネントが配置してあり、ソフトウェアで EG アキュムレータの値をステータス・レジスタから読み出し、対数-リニア変換した結果を 48 kHz サンプリングのオーディオ・データとして SPDIF 出力しています。

上の方にある「acc9」は、中身を verilog で記述したクロック・イネーブル付きの 9 ビット・アキュムレータで、EG アキュムレータとして使っています。 中身の詳細は省略します。

下の方にある T-FF がアタック/ディケイの切り替えのためのフリップ・フロップで、出力が「1」の場合がアタック・モード、出力が「0」の場合がディケイ・モードとなります。

EG アキュムレータの加算入力に 2-to-1 マルチプレクサが接続してあり、アタック・モードの場合にはアキュムレータ出力の反転 (1 の補数) を 3 ビット右シフトしたものが加わり、ディケイ・モードでは定数の 9'b0_0000_0001 が加わります。

ハイレートの場合には、さらにシフト量を変化させるメカニズムが必要になりますが、ローレート専用なので、シフト量は固定です。

アタック/ディケイの切り替えは、EG アキュムレータ出力が

- アタック・モード時 : 9'b0_0000_0001 になること (アタック・ピーク)

- ディケイ・モード時 : 9'b1_1111_1110 になること (最大減衰)

を検出して T-FF を反転させることで実現しています。

リソース使用量は、SPDIF_Tx コンポーネントも含めて回路全体では

- マクロセル : 100 個 (52.08 %)

- PLD : 48 (100 %)

- UDB : 24 (100 %)

と、UDB を 100 % 使い切る結果となっています。

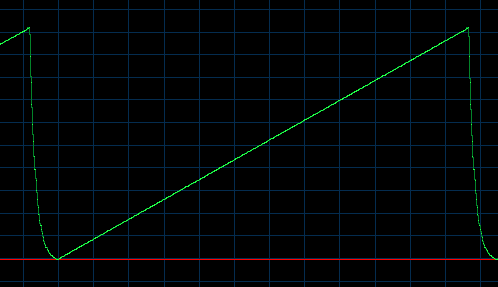

SPDIF 経由でキャプチャした EG アキュムレータ値を波形編集ソフトで表示させたものを下に示します。

ローレートの範囲では最も速いレートの、RATE = 12、Rof = 3 の設定で、1 周期分の範囲を表示してあります。 (アタック・レートとディケイ・レートは同じ値)

のこぎり波のように見えていますが、右上がりの直線部分はディケイ部分で、曲線的に立ち下がっているのがアタックの部分です。

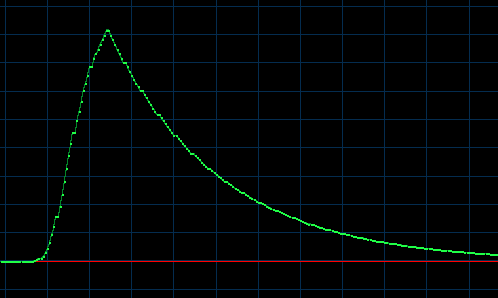

対数-リニア変換した結果を下に示します。 時間軸のスケールは上のグラフと同一ではありません。 アタック付近を拡大して見ています。

見慣れたエンベロープ・カーブの形状になっています。