FPGA 版 FM 音源 (84) -- TX7 (OPS) 測定 (11)

EG のアタック部分をプログラムで再現することができました。 やはり「ゴンペルツ曲線」でした。 (→参考記事)

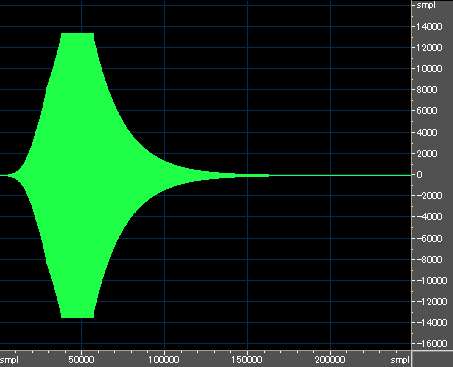

まず、アタック/リリースの「エンベローブ波形」をキャプチャしたものを再掲します。

このアタック部分の波形の値を 2 を底とする対数に変換した値を y 軸としてプロットしたグラフを下に示します。

後述の回路が簡単になるように R1 = 44 と選んでいます。

後に示す回路に相当するプログラムによるシミュレーション結果が赤色のトレースで、TX7 出力をキャプチャしたものを青色のトレースで表示してあります。

アタックの最初の部分と、サンプル・インデクス 20000 を超える部分の 2 箇所を除いて、キャプチャ結果とシミュレーション結果とは、ほぼ一致しています。

アタックの最初の部分については、OPL とは違って、サイン波出力部から「DC」を出せず、オペレータを「キー・シンク」のモードで動作させる限りサイン波のゼロクロス部分から始まるので正確な EG 出力値を知ることはできません。

サンプル・インデクス 20000 を超える部分は、EG の「L1」に到達して、R2/L2 および R3/L3 のセグメント (サステイン) に移行する部分です。 シミュレーションではアタック部分のみを生成しているので、不一致が生じます。

シミュレーション・プログラムの仕様を回路図で表現すると下のようになります。

EG 値としてはサンプリング・クロック 32 個分、同一の出力値が続きます。 図では 1/32 のプリスケーラで表現していますが、実際は 1/16 プリスケーラと 4/8 のレートのレート・マルチプライアで実現されていると思われます。

EG アキュムレータは整数部 4 ビット、小数部 8 ビットで、フィードバックの右シフト量も 8 ビットとなっています。 この条件でキャプチャ結果とほぼ一致します。

これを、たとえば、小数部を 1 ビット増やして 9 ビットとし、フィードバックするデータの幅も 5 ビットにすると、一致度が下がります。