FPGA 版 FM 音源 (41) -- YMF297 (OPN3/OPL3) 測定 (6)

OPL3 のオペレータの EG 部分とピッチ発生部分とを除く、サイン波生成部分を Verilog-HDL で記述し、ModelSim でシミュレーションしてみました。

出力波形は、ディジタル・データとして、実チップ (OPL3 モードの YMF297) の出力を S/PDIF 経由でキャプチャしたものと完全に一致しました。

キャプチャしたデータがあるのは FB (FeedBack) = 0 で WS (Wave Select) = 0 〜 7 の波形と、WS = 0 (普通のサイン波) で FB = 0, 3, 4, 5. 7 の場合です。 その他の組み合わせについてはキャプチャしていないので比較していませんが、おそらく一致すると思います。

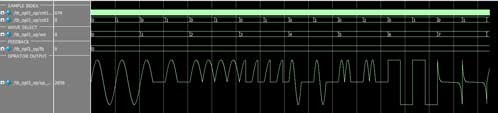

FB = 0 で WS = 0 〜 7 まで変化させた場合のシミュレーション結果を下に示します。 (画像をクリックすると拡大します)

一番下のトレースがオペレータ出力を「アナログ」表示したものです。 上から 3 番目のトレースが WS の値で、ひとつの WS の設定に対して 2 周期分の波形を生成しています。

シミュレータは

ModelSim ALTERA WEB EDITION 6.3g_p1

を使っています。

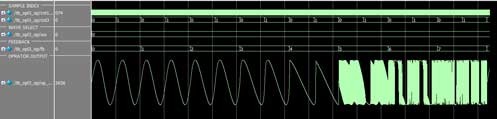

WS = 0 で FB = 0 〜 7 まで変化させた場合のシミュレーション結果を下に示します。 (画像をクリックすると拡大します)

上から 4 番目のトレースが FB の値です。

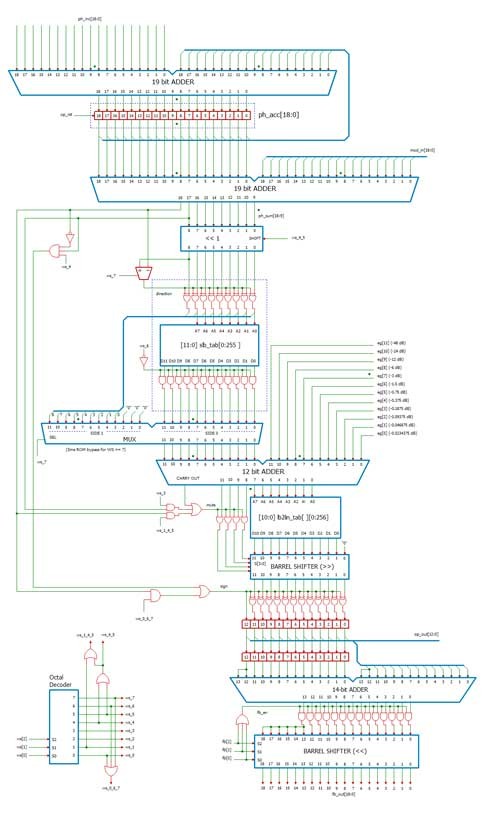

なるべくバス表示にせず、各ビットを個別に書いた回路図を下に示します。 (画像をクリックすると拡大します)

ビットをバラして書いてあるのでサイズが大きく、拡大画像は横 1200 ピクセル × 縦 1982 ピクセルあります。

フィードバック経路は内部にはなく、フィードバック出力 fb_out[18:0] と変調入力 mod_in[18:0] とを外部のワイヤで接続する必要があります。

この回路は「原理的」なものを示していて、「実用的」ではありません。

「パイプライン」ではなく、完全に「パラレル」な形で表現されており、「レジスタ」は ph_acc, op_out, out_dly の 3 本しかなく、ph_acc レジスタと op_out レジスタとの間には、加算器 2 段、ROM 2 段、バレルシフタ、マルチプレクサ、その他のゲートなどの多数の組み合わせ回路が縦続に接続されています。

FPGA の内蔵 RAM を ROM として使う場合に、完全非同期の構成が取れない場合には RAM ブロックには「速い」クロックを供給して、同期化による遅れを小さくする必要があります。

Verilog-HDL のソースについては次回に掲載します。