FPGA 版 FM 音源 (26) -- EG シミュレーション (2)

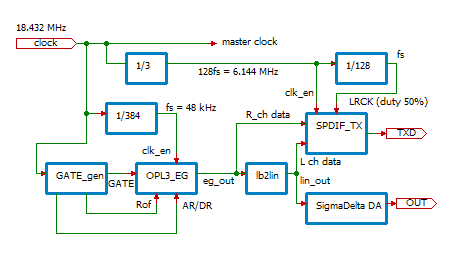

FPGA (無印 Cyclone) 上にインプリメントした回路のトップ・レベルのブロック・ダイアグラムを下に示します。

実際には 2010 年 12 月 2 日の記事 (→こちら) のトップ・レベルの回路図に追加して実現しています。

もとの回路のゲート信号発生用カウンタと、シグマ=デルタ DAC のみを利用し、ほかの部分は新たに作成したものです。

ゲート信号発生部では、ゲート・パルスを 1 個発生するごとに Rof および AR/DR の値を更新し、全 64 パターンを発生させています。 ただし、AR/DR = 0 については EG 部で対応していないので、有効なのは 60 パターンのみです。

EG 出力はリニア値に変換したものをシグマ=デルタ DAC によりアナログ値として出力するほかに、SPDIF 送信モジュールによりディジタル・データとして出力しています。

サンプリング速度変換やボリューム・コントロールなどが行われない SPDIF オーディオ入力デバイスを使用すれば、ディジタル・データとして 1 ビットも損なうことなく PC に取り込むことができます。

FPGA のクロックとしては、18.432 MHz を使用し、3 分周して SPDIF 出力モジュールで必要とする 128fs = 6.144 MHz (のクロック・イネーブル信号) を生成し、384 分周してサンプリング周波数 48 kHz のクロック・イネーブル信号を作り出しています。

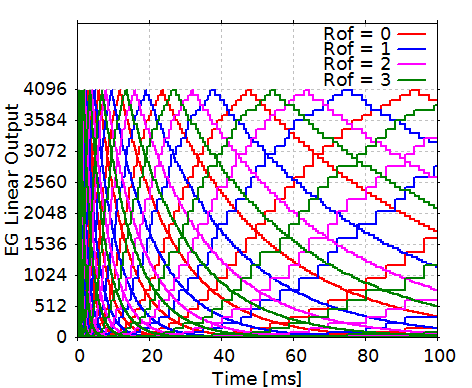

SPDIF 経由でキャプチャした結果の EG リニア出力値のグラフを下に示します。

ゲート ON から 100 ms までを示しています。

Rof の値により色分けしてあります。

「Rof = 3」 などのグラフの凡例 (legend) の下付近の 50 〜 90 ms 付近にアタックのピークを持つトレースが AR/DR = 6 に対するエンベロープで、それより長いエンベロープは一部分しか見えていません。

ゲート・パルスの間隔が約 4 秒なので、ディケイ・タイムが数十秒におよぶ領域は直接確認できていませんが、一番長いアタック・タイム約 3 秒の AR = 1、Rof = 0 については確認できました。