FPGA 版 FM 音源 (54) -- YMF297 (OPN3/OPL3) 測定 (19) -- EG クロック・プリスケーラ (6)

EG をディケイの DR = 13、Rof = 0〜3 の範囲に限りハイレートに対応させました。

アタックに関してはハイレートでは EG アキュムレータ部に (パラレルな実現では) バレルシフタが必要になりますが、ディケイについては EG アキュムレータの増分の定数が「1」と「2」の 2 種になるだけなのでハードウェアの増加量を抑えられます。

まず、EG アキュムレータ部でシフト量を変化させる「SFT_SEL」信号の生成は、2011 年 2 月 1 日付けの記事 (→こちら) の回路が使えます。

記事では SFT_SEL をいったん生成してから CLK_EN を作成していましたが、今回の回路ではクロック・プリスケーラ信号から CLK_EN を生成するので、SFT_SEL の生成はそれとは別に行なうことになります。

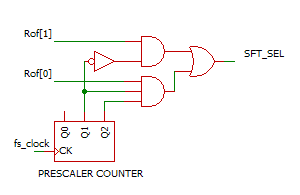

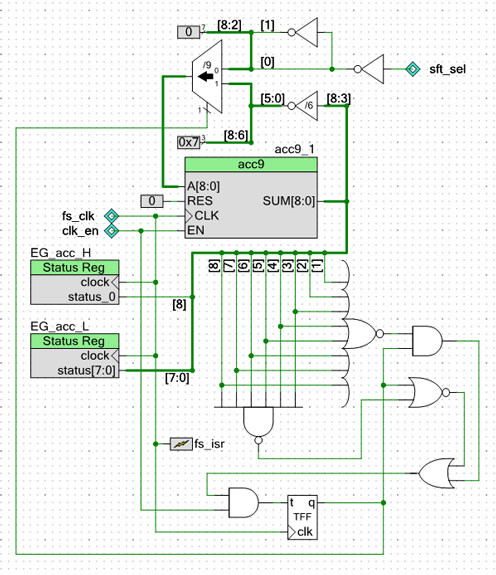

SFT_SEL 生成部のみを抜き出した回路図を下に示します。

このオクタル (8 進) カウンタはハイレート用として新たに設ける必要はなく、ローレート用のプリスケーラの 2 段目、3 段目のカウンタ部分から配線を引き出して共用することができます。

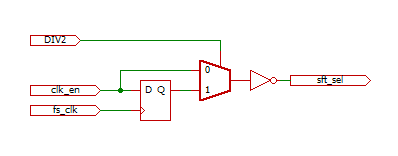

また、2011 年 2 月 1 日付けの記事では「SFT_SEL」から「CLK_EN」を作り出していましたが、逆に下の回路で「CLK_EN」から「SFT_SEL」を作り出すこともできます。

ただし、CLK_EN 作成回路はハイレートの場合でも RATE = 12 に相当する出力を出し続ける必要があります。

「DIV2」信号はプリスケーラ・コンポーネントの初段の「DIV2」出力です。 (プリスケーラ回路全体で見ても初段)

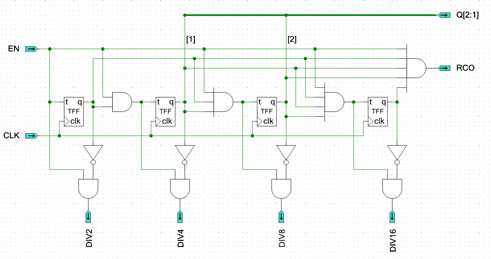

プリスケーラの Q1、Q2 を引き出す改造を施したコンポーネント「psc4h」の回路図を下に示します。 (図をクリックすると拡大します)

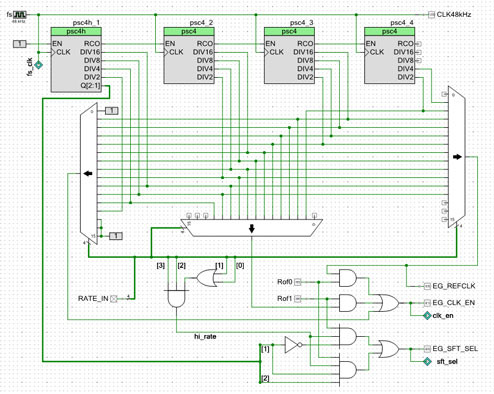

プリスケーラの初段のみに「psc4h」を使い、SFT_SEL 生成部を追加した回路図を下に示します。 (図をクリックすると拡大します)

ディケイ部分に +1 と +2 の切り替え機能を追加した EG アキュムレータ部分の回路図を下に示します。 (図をクリックすると拡大します)

ハイレートでのディケイ部の増分が +1 と +2 の 2 種になったことにより、場合によっては EG アキュムレータの値が 9'b1_1111_1110 を「飛び越える」可能性が生じ、8 ビット分の「1」を検出しているとアタック/ディケイ切り替えがうまく動作しなくなります。

そこで、NAND ゲートによる検出を eg_acc[8:3] の範囲に狭めています。

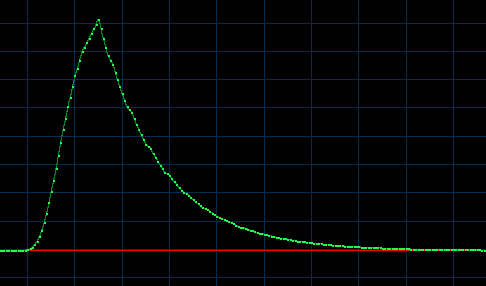

EG 回路を RATE = 13、Rof = 3 の設定で動作させて、リニア出力をキャプチャした結果を下に示します。

アタック部分には SFT_SEL に対応する回路を組み込んでいないので RATE = 13、Rof = 0 の設定に相当するアタック・カーブとなっています。

ディケイ部分は、ハイレートでの Rof = 3 の設定の特徴の

- 6 サンプル連続で振幅方向に 2 ステップ分の変化

- 2 サンプル連続で振幅方向に 1 ステップ分の変化

の繰り返しとなっているのが分かります。