PSoC 4200 Prototyping Kit (13)

UDB (Universal Digital Block) 内の「データパス」(datapath) モジュール 2 個と、サンプリング・タイミング発生用の TCPWM コンポーネント 1 個を使って (オーディオ帯域の) 16 ビット・データ入力シグマデルタ変調型 DAC を作りました。

シグマデルタ変調器そのものはデータパス「だけ」で作成できるのですが、サンプリング・タイミングのコントロールを UDB 内のロジックで作成するとリソースの消費量が多くなってしまうので、「ハードマクロ」の TCPWM コンポーネントで LRCLK 相当のタイミング発生をすることにしました。

ステレオ、つまり同じサンプリング・タイミングで動作する 2 ch DAC を構成する場合には、TCPWM コンポーネントは左右 ch 共通に使えるので、データパス・モジュールに関しては 4 個 (UDB 4 個分) だけで実現できます。 4 個の UDB 内の他のリソース (マクロセル、PLD プロダクト・ターム、ステータス/コントロール・レジスタ) は全く消費しません。

ストレート・バイナリ形式、つまり 16 ビットの符号なし整数

- 最小値 0x0000 (0)

- 最大値 0xFFFF (65535)

およびオフセット・バイナリ形式の 16 ビット符号付き整数

- 負の最小値 (絶対値最大) 0x0000 (-32768)

- ゼロ 0x8000 (0)

- 正の最大値 0xFFFF (32767)

の入力データについては、シグマデルタ変調器は単なる 16 ビット「アキュムレータ回路」で実現できます。

このとき 16 ビット ALU のキャリー出力が目的の 1 ビット DAC 出力となります。

一般に使われる 2 の補数表現の MSB (ビット 15) を反転すればオフセット・バイナリ形式になるので、この変換はソフトウェアで行う方針で、ハードウェアではストレート/オフセット・バイナリ形式で扱うことにします。

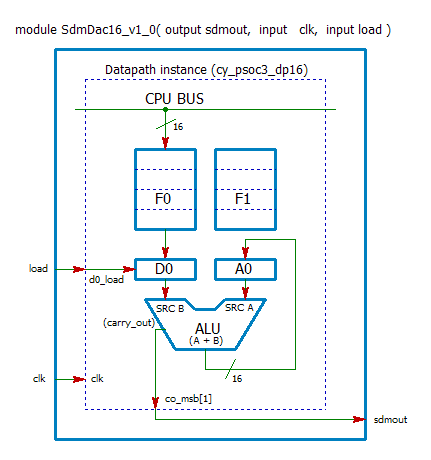

データパス・モジュールの構成は下の図のようになります。

外側の青色の太線で囲ってある部分が作成する SdmDac16 コンポーネントの部分を表し、その実体は Verilog モジュールの SdmDac16_v1_0() です。

ここで、サフィックスの「_v1_0」はコンポーネントの命名規則によって付加が義務付けられているバージョン番号で、「v1.0」の意味です。

内側の青色の破線で囲まれた部分がデータパス・モジュールのインスタンス部分で、16 ビット幅なので実際には 8 ビット ALU を持つデータパス・モジュール 2 個を消費しています。

コンポーネントの端子との間にはランダム・ロジックは存在せず、wire で接続しているだけです。

データパス関連の文書での ALU の表現と違って左右が反転、つまり左側の入力が「SRC B」、右側の入力が「SRC A」となっていますが、これは図を描く都合によるものです。

回路の動作としては、まず d0_load 入力の立ち上がりを検出した次のクロック・エッジでレジスタ D0 に FIFO0 (F0) から新しいデータを取り込みます。

それ以外の条件では D0 は変化しません。

ALU では常に (D0 + A0) の計算を行って、結果をアキュムレータ A0 に格納しています。

ALU のキャリー出力をコンポーネントの sdmout 端子に出力し、外部に設けた LPF を通してアナログ信号を得ます。

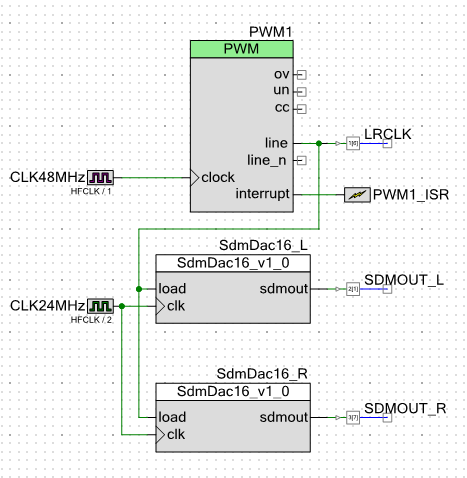

SdmDac16 コンポーネントを 2 個配置してステレオ構成とした回路を下に示します。

PSoC42xx ではハイスピード・クロックの系統はひとつしかなく、CPU クロックも周辺回路のクロックも同じ HFCLK から分周して得ることになります。

UDB は 48 MHz クロックでは動作できないので、CPU クロックを 48 MHz に選ぶと UDB はその 1/2 の 24 MHz がクロックの最大周波数となります。

ステレオの 2 系統の load 入力、clk 入力についてはパラレルに接続します。

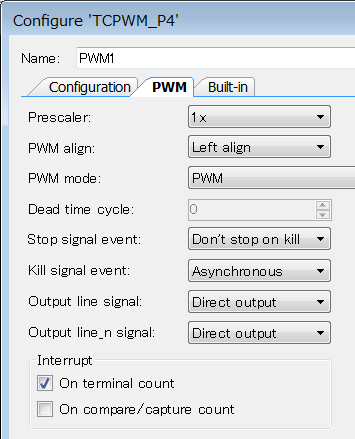

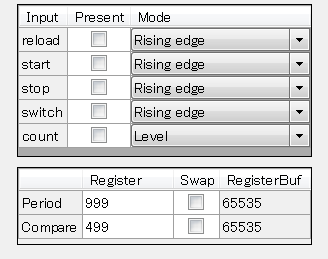

サンプリング周波数を 48 kHz とする場合、LRCLK 発生用の PWM モードの TCPWM コンポーネントの設定は下のようにします。

48 MHz クロックを 1000 分周して 48 kHz の LRCLK を得ています。

TC (Terminal Count) のみ割り込みを許可しているので、LRCLK 出力の立ち上がりエッジの直後に割り込みが掛かります。

割り込みハンドラ内ではメイン側から出力サンプル・データを引き取り、SdmDac16 コンポーネントの F0 レジスタに書き込む処理を行います。 (左右 ch それぞれ)

SCB (Serial Communication Block) の SPI コンポーネントを利用してシリアル DAC にも同時にデータを送出する場合には、PWM コンポーネントの CC (Compare/Capture) 割り込みも許可して、右 ch のデータを送出するタイミングでも割り込みが掛かるようにします。

コンポーネントの作成方法の概略や、Verilog ソースについては次回にまわします。