アナログシンセの VCO ブロック (53) -- マルチ出力アンチログ回路の測定 (3)

Spice の Ebers-Moll モデルでは、バイポーラ・トランジスタが大電流領域において理想 PN 接合の特性からズレてくる効果を、理想 PN 接合による「真性トランジスタ」の外部に直列抵抗を接続することにより表現しています。

直列抵抗の「実体」としては、端子のリードフレーム/ボンディング・ワイヤ/メタル配線や、(PN 接合部ではない) 半導体のバルク抵抗などです。

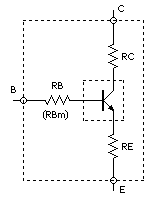

左の図のように、内側の破線で囲った部分を理想 PN 接合特性の真性トランジスタ部分として、そのベース、エミッタ、コレクタにそれぞれ「オーミック」(Ohmic) つまりオームの法則にしたがう「普通」の抵抗を直列に接続したものをシミュレーション上のトランジスタのモデルとしています。

実際には、Spice では「改良型」である Gummel-Poon モデルを主に使用しますが、その場合でもエミッタ直列抵抗 RE とコレクタ直列抵抗 RC は受け継がれ、ベース直列抵抗は 2 分割されて「外部抵抗」 RBm とモデル内部で使われるベース抵抗に分けられます。

この外部直列抵抗による影響としては、エミッタ抵抗 RE では、エミッタ電流 IE により抵抗両端に (IE · RE) だけの電圧降下が生じ、トランジスタ・モデルの BE 端子間に加えられる電圧 VBE から、この電圧降下分だけ目減りした電圧が内部の真性トランジスタの BE 端子間に加わることになります。

同様にして、ベース直列抵抗 RB (RBm) についても (IBE · RB) の電圧降下が生じます。

このエミッタ抵抗 RE とベース抵抗 RB による影響は直流電流増幅率 hFE (βF) を媒介として相互に変換可能で、

となります。

ベース抵抗 RE、エミッタ抵抗 RB ともに存在する場合に、ベース抵抗 RB = 0 として RB の寄与をエミッタ抵抗 RE 側に取り込んだ値を RE′ とすると、

となります。 (ここではプライム記号「′」は「微分」の意味ではありません)

このようにして、ベース抵抗、エミッタ抵抗の寄与を全てエミッタ抵抗側に集めてベース抵抗 RB = 0 とした場合の、典型的なアンチログ回路を左に示します。

この図で、トランジスタは理想的な真性トランジスタを表すものとし、コレクタ直列抵抗 RC は回路動作には影響しないのでゼロとしています。

まず、Q1 側の

IC1 = Iref = Vref / Rref

に対する式を立てると、

となります。

ここで具体的な値を求めると、RE は 1 Ω 程度、Iref については、アンチログ出力電流のレンジを 1 μA 〜 1 mA としてその相乗平均の 32 μA 程度に選ぶとすると、エミッタ抵抗 RE1′ による電圧降下は

Iref · RE1′ = 32 [μA] · 1 [Ω] = 32 μV

となり、半音 (100 セント) に対する電圧が約 1.5 mV ということから計算すると 32 μV は約 2 セントの誤差にしかならないので、簡単のため RE1′ による誤差は無視して、

とします。

Q2 側のアンチログ出力電流 Iout′ に対する式を立てると、

となります。 これに先の Iref の式を代入すると、

となります。

エミッタ直列抵抗 RE2 = 0、つまり誤差を含まない理想特性を Iout とすると、

となり、両者の比をとると、

と表されます。

この式から、アンチログ出力誤差がエミッタ直列抵抗によるものと仮定した場合の直列抵抗値の概算値を測定結果から求めてみると、

から、

0.75 [mV] = Iout′ · RE2′ = 1 [mA] · RE2′

RE2′ = 0.75 [Ω]

となります。

Iout′ の比の式での指数関数をテイラー展開すると、

と表されます。

これを 2 次以上の項は無視して、1 次の項までで打ち切ると、以前に求めたリセット型 VCO でのリセット時間に起因する誤差、およびベース結合型アンチログ回路でのベース電流に起因する誤差の式 (以前の記事 → こちら)

と同じ形になります。 (f′ と f との差が小さいとして)

アンチログ出力誤差の出方を近似するふたつのモデル

- リセット時間誤差近似 (下図の青いプロット)

- エミッタ直列抵抗誤差近似 (下図の赤いプロット)

での誤差カーブと、実際の測定データとを比較した近似誤差をプロットしたのが下の図です。

リセット時間誤差近似については全域で近似誤差が小さい状態にはできないので、MIDI ノート・ナンバー 1 から 100 までの測定データに対してフィッティングしたもので、エミッタ直列抵抗誤差近似に対しては MIDI ノート・ナンバー 1 から 127 までの測定データを使ってフィッティングしたものです。

エミッタ直列抵抗誤差近似では、全域に渡り 1 セント以下の近似誤差で測定データの誤差の出方を「説明」できていることが分かります。

リセット時間誤差近似にしても、約 8 オクターブ分は近似誤差は小さく、最大の近似誤差でも 5 セント程度となっています。

リセット型 VCO のリセット時間誤差は Franco の補償により抵抗 1 本で簡単に補正できるので、現在未実装のもう 1 系統のアンチログ出力にはリセット型 VCO を実装して、Franco の補償でどこまで誤差を少なくできるかを試してみようと思っています。