MS-20 タイプの VCF (4)

VCF で可変抵抗素子として使う飽和状態のトランジスタに、ベース結合アンチログ回路を組み合わせて LTspice で ON 抵抗の変化をシミュレーションしてみました。

トランジスタのエミッタ/コレクタは、信号の入力/出力端子として使われるので、直接には信号を入力しないベースを制御端子としてドライブするベース結合アンチログ回路と、とても良くマッチングします。

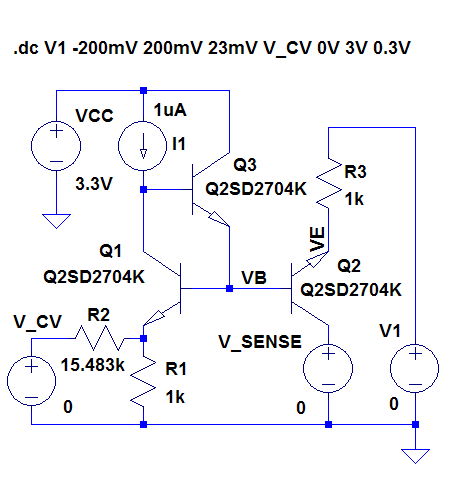

シミュレーションの回路図を下に示します。

回路の右半分は、前回までのトランジスタ回路と同じですが、これまでのアンチログ回路の説明と合わせるために、トランジスタ番号を「Q2」と変更しています。

回路の左半分は、これまでのベース結合アンチログ回路と同じで、従来は Q2 のコレクタをアンチログ電流出力として使っていたのを、飽和状態のトランジスタ Q2 に置き換えただけのものです。

Q2 は飽和状態なので、電流増幅作用は期待できず、Q2 のベース電流は多めの値となります。

ベースをドライブする Q3 にも forward hFE の大きいミューティング用トランジスタを使ってドライブ能力を上げて対処しています。

Q2 は「逆方向」に使われているので、Q1 も逆方向にしたほうがバランスは良くなります。

理想的な Ebers-Moll モデルでは、正/逆、どちらでも hFE が変わるだけで、特性に変化はないはずです。

実際の回路では、そうとは限りませんから、正/逆で変化があるかどうか試してみたいと思っています。

CV の分圧比は、回路図の定数で、約 0.3 [V/oct] となっており、CV = 0 〜 3 V とスイープして 10 オクターブに渡る変化を見ています。

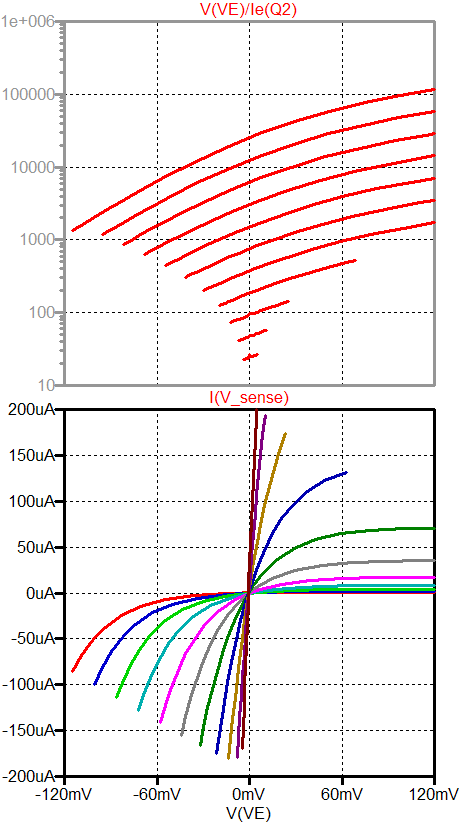

結果のグラフを下に示します。

前述の「論文」での ON 抵抗を表す式の結果だけを示すと、

となります。

この式には、ベース電流 () と reverse hFE (

) が含まれおり、一見、トランジスタの個体差で

が変動すると ON 抵抗も変動するように思えますが、実はそんなことはありません。

両者の積 は、逆方向の接続で流しうるコレクタ電流の最大値で、ベース結合アンチログ回路では、実際のコレクタ電流ではなく、この仮想的な電流をコントロールする形になっています。

上の回路では Q1 に流している電流は 1 μA ですから、CV = 0 V の時に Q2 側には 1 μA、CV = 3 V の時に 1 mA 流れるのに相当する状態になります。

したがって、ON 抵抗は CV = 0 V の場合、

26 [mV] / 1 [μA] = 26 [kΩ]

CV = 3 V の場合、

26 [mV] / 1 [mA] = 26 [Ω]

となります。

上のシミュレーション結果でも、ほぼ、この理論値と一致した値になっています。

細かな直線性は分かりませんが、少なくとも 10 オクターブに渡るレンジの ON 抵抗の変化が得られています。

VCO の場合には、「発音源」ですから、高い音はピアノの最高音 4186 Hz が出ればいいと割り切れば 4 kHz までしか発振しない VCO でも使えます。

一方、LPF タイプの VCF の場合には、可聴域内で「素通し」状態にするにはカットオフ周波数を 20 kHz にする必要があり、4 kHz までしか「開かない」VCF では使い物になりません。

10 オクターブのレンジがあれば、カットオフ周波数 20 Hz 〜 20 kHz をカバーできます。

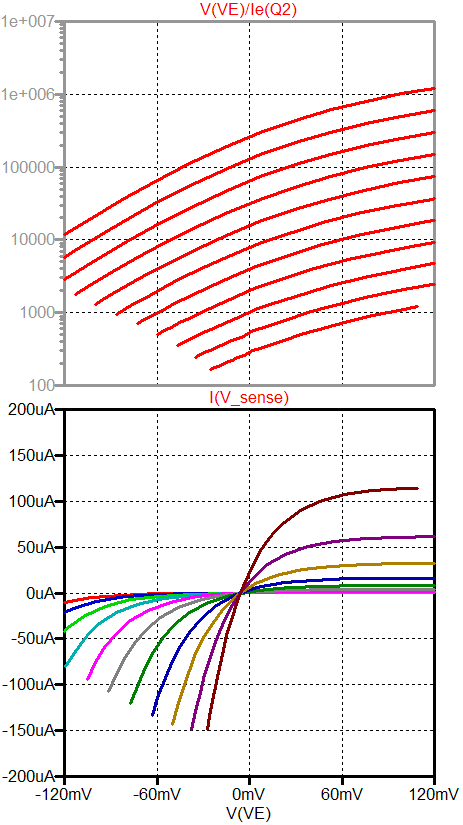

上に示したシミュレーション回路の Q1 と Q2 を 2N3904 に置き換え、電流源 I1 の電流値を 0.1 μA に絞った回路でのシミュレーション結果を下に示します。

ベース電流のドライブ能力が必要なため、Q3 は 2N3904 にはせず、高 hFE の 2SD2704K のままにしてあります。

また、I1 を 1 μA にしておくと、ON 抵抗の小さい部分で無理な状態となり、このグラフの表示のレベルでも明確な直線性の悪化が認められるので、1/10 の 0.1 μA に絞っています。

したがって、ON 抵抗の理論値は 260 Ω 〜 260 kΩ となりますが、シミュレーション結果では約 300 Ω 〜 300 kΩ となり、少し差が見られます。