OTA/VCA/PGA を使用した 2 次特性 VCF (8)

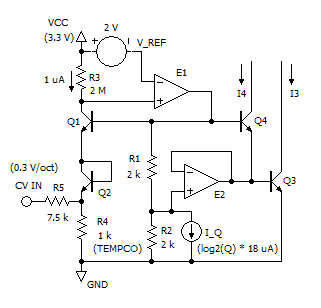

3.3 V 単一電源での実現を念頭に置いたベース結合型のアンチログ回路を下に示します。

前回同様、LTSpice での回路シミュレーションが目的なので、実際に動作させるには追加の回路要素が必要になります。

アンチログ出力側の Q3、Q4 周辺の回路は前回のエミッタ結合型の回路と基本的には同じです。

エミッタ結合型の回路では Q4 のベースをグラウンドに固定し、Q3 のエミッタを OP アンプ出力でマイナス側に引っ張っていますが、ベース結合型の回路では、Q3 のエミッタをグラウンドに固定し、Q4 のベースを OP アンプでプラス側に引っ張っているところが違っています。

ベース結合型の回路では、アンチログ回路出力電流範囲の最小値の電流を Q1、Q2 側に流します。

2 MΩ の抵抗での電圧降下がリファレンス電圧の 2 V になるように OP アンプによる定電流回路が動作しますから、2 [V] / 2 [MΩ] = 1 [μA] が Q1、Q2 側に流れます。

前回のエミッタ結合型回路では CV のサミング・アンプ部は省略していましたが、ベース結合型回路では抵抗分圧回路により CV のスパンを合わせるので、CV としては「仕上がり」の約 0.3 V/oct のスパンで入力します。

普通のベース結合アンチログ回路では、Q1 のエミッタ抵抗が 1 kΩ の場合、分圧用抵抗は約 15 kΩ となりますが、この回路では 2 Vbe 分をドライブしなければならないので、分圧抵抗の値は半分の 7.5 kΩ となっています。

(kT/q) の因子による温度特性の補償のためには、Q1 のエミッタの 1 kΩ を温度補償抵抗 (TEMPCO) にします。

この部分は抵抗分圧回路となっているので、TEMPCO の温度特性が薄められる形となり、規定の 3300 ppm/K では補償量が十分ではなくなります。

トータルで 3300 ppm/K の特性を得るためには、

3300 [ppm/K] * (R4 + R5) / R5

= 3300 * 8.5e3 / 7.5e3 = 3740 [ppm/K]

とする必要があります。

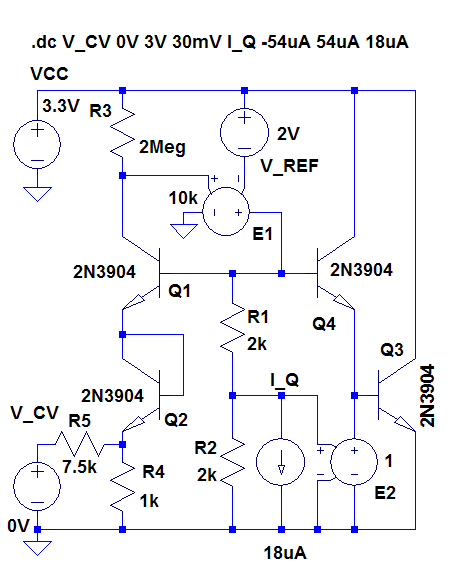

LTSpice シミュレーション用の回路図入力を下に示します。

Q を決める電流は -54 μA から 54 μA まで 18 μA ステップで変化させています。

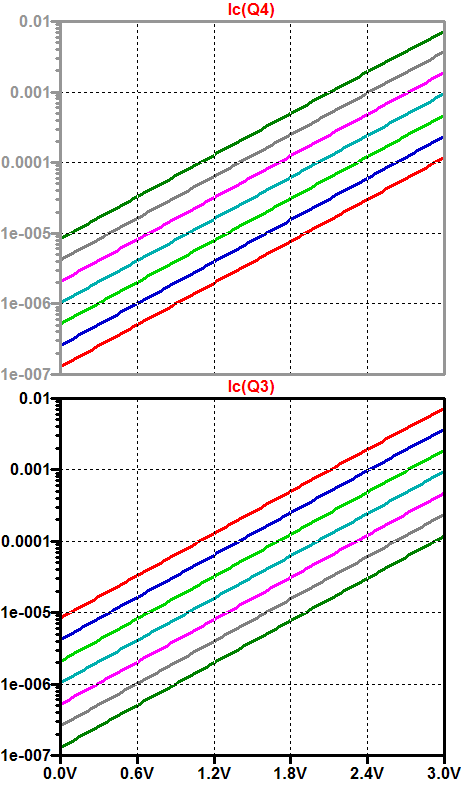

LTSpice の DC スイープ解析結果のグラフを下に示します。

カットオフ周波数を決める CV (横軸) に対して Ic3、Ic4 (縦軸、対数目盛り) をプロットしてあります。

グラフのトレースの色と IQ の値との対応表を下に示します。

| トレース 番号 |

トレース の色 |

I_Q [uA] |

|---|---|---|

| 1 | 赤 | -54 |

| 2 | 青 | -36 |

| 3 | 明るい緑 | -18 |

| 4 | シアン | 0 |

| 5 | マゼンタ | 18 |

| 6 | 灰 | 36 |

| 7 | 暗い緑 | 54 |

ちょっと緑と区別がつきにくいですがシアン色のトレースが IQ = 0 の場合で、Ic3 と Ic4 の値は等しく、1e-006 A (1 μA) から 0.001 A (1 mA) まで変化しています。

前回のエミッタ結合型アンチログ回路のシミュレーションでは反転増幅器であるサミング・アンプを省略してトランジスタのベースに直接 CV を入力していたのでグラフは右下がりになっていましたが、今回のベース結合回路では CV 入力部の分圧抵抗を省略していないので、「仕上がり」のスパン 0.3 V/oct の特性で CV = 0 V で出力電流最小、 CV = 3 V で出力電流最大となっています。

グラフの右上がり、右下がりの違いを除けば、IQ の変化に対して前回の結果と同様になっています。