OTA/VCA/PGA を使用した 2 次特性 VCF (10)

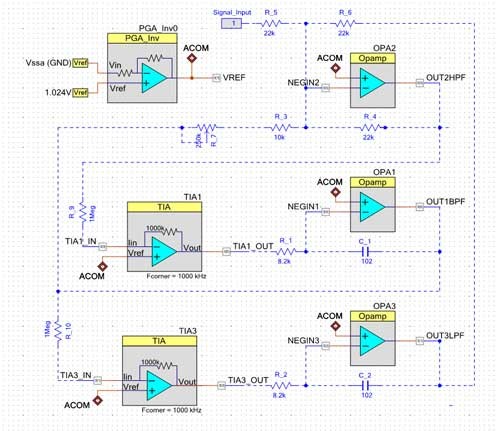

PSoC5LP 内蔵 OP アンプ/TIA (Trans-Impedance Amplifier) を使った状態変数型 2 次フィルタのトップ・レベルの回路図を下に示します。 (図をクリックすると拡大します)

外部回路も記述してあります。

回路としては、ゲイン -1 倍の反転型 PGA (Programmable Gain Amplifier) により、内蔵 Vref の 1.024 V を元に約 2 V 程度の電圧を発生させ、OP アンプ/TIA のアナログ・コモン電圧として利用しています。

したがって、クリップせずに扱える信号レベルは約 4 Vp-p となります。

あとは、OP アンプ 3 個と TIA 2 個の、それぞれの入出力をピンに引き出してあるだけです。

OP アンプ入出力は、アナログ・バスを経由して任意のピンに引き出すことができますが、特定の専用のピンに対してはバスを介さない「直通」の経路を持っています。

特に OP アンプはスペック上では最大 25 mA の出力電流ですが、これは専用ピンに出力した場合に限られます。

そのため、OP アンプ出力は専用ピン (P0.0 / P0.1 / P3.6 / P3.7) に割り付け、入力もなるべく専用ピンに割り付け、なるべくアナログ・バスのリソースを消費しないようにするのが望ましいです。

しかし、いくつかのピンは ADC を使用する際の Vref のバイパス・コンデンサを接続する端子としても使われているので注意する必要があります。

それは、

- P0.4 — SAR ADC0 EXTREF

- P0.2 — SAR ADC1 EXTREF

- P0.3 — デルタ・シグマ ADC などの EXTREF0

- P3.2 — デルタ・シグマ ADC などの EXTREF1

の 4 つです。

PSoC5LP Prototyping Kit では、ターゲット・ボード上に、この 4 つ全てに対して 1 μF の積層セラミック・コンデンサが実装されており、リファレンス電圧のバイパス用途以外には使いづらくなっています。

SAR ADC0/1 と、デルタ・シグマ ADC を同時に利用する可能性は十分考えられるので、ADC0/1 EXREF と EXTREF0 についてはそのまま残し、P3.2 の EXREF1 についてはボード上からコンデンサを除去して他の用途に開放することにしました。

上の回路図でも OPA3 については反転入力である P3.2 がフリーであることが前提です。 P0.2 / P0.3 / P0.4 については使用していません。

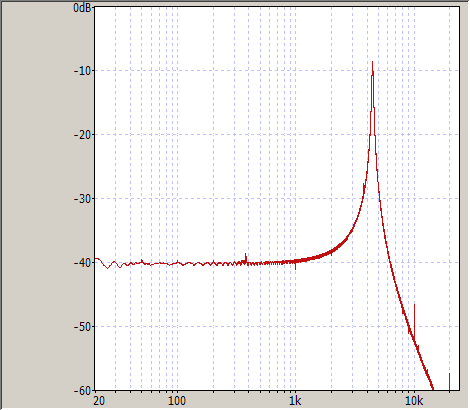

上の回路で、BPF 出力からのフィードバック抵抗を 2 MΩ として Q が約 90 となる設定で、「リニア周波数スイープ」+「ピーク・ホールド」で求めた周波数特性を下に示します。

BPF 出力からのフィードバック回路を「オープン」にすれば、原理上は Q が無限大になって発振することになりますが、実際にはオープンにしても発振には至りませんでした。

1 個余っている SC/CT ブロックを利用して反転型 PGA を構成し、BPF 出力の反転出力を作って「ポジティブ」フィードバックの経路を追加すると発振することは確認できました。