FPGA 版 FM 音源 (35) -- YM2151 (OPM) 測定 (3)

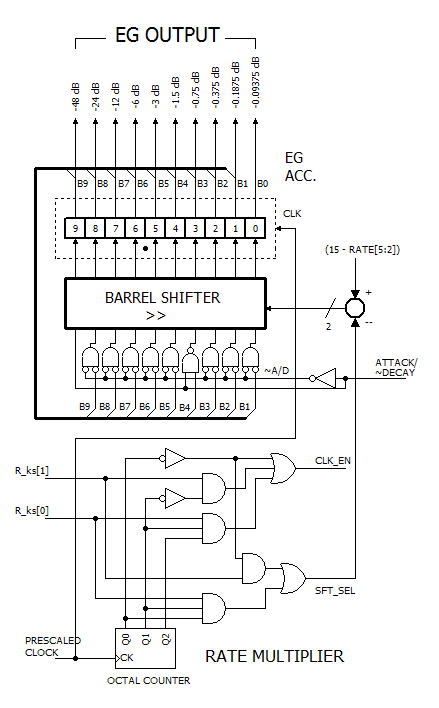

2011 年 2 月 11 日付けの記事 (→こちら) での YMF262 (OPL3) のアタック計算回路と同様の回路を、YM2151 (OPM) に対して書いてみました。

原理を示すもので、細かいコントロール等については表現してありません。

EG アキュムレータのビット幅の違いと、レート・マルチプライアの部分が、CLK_EN 出力は 3 ビット・カウンタ、SFT_SEL 出力は 2 ビット・カウンタを使った回路になっている部分が違います。

OPL3 の図では省略した、アタック/ディケイ/リリースの計算の切り替え部分も示してあります。

アタックの計算では、EG アキュムレータに、その内容の 1 の補数 (ビットごとの反転) を取ったものを右シフトして足し込みます。

一方、ディケイとリリースの計算では、EG アキュムレータに固定ビット・パターンを足し込んでいきます。

そのアキュムレータに足し込む値の切り替えを、バレル・シフタ入力に接続した NAND ゲートと NOR ゲートで行っています。

OPM の場合には、 EG レートは音色パラメタとしては 5 ビットが割り当てられており、そのパラメタ値を「R」、キー・レート・スケーリング値を「RKS」として、スケーリング補正ずみの実効レート値「RATE」は

RATE = (2 * R) + RKS

の式を計算して求めます。

計算結果が 63 を超える場合には 63 にクリップします。

「リリース・レート」(RR) は 4 ビットなので、2 倍して 5 ビット幅に揃えてから上の式を適用します。

実効レートの上位 4 ビットはハイ・レートの場合はバレル・シフタのシフト量の決定に使われ、ロー・レートの場合はクロック・プリスケーラの制御に使われます。

下位 2 ビットはレート・マルチプライアに入力されます。

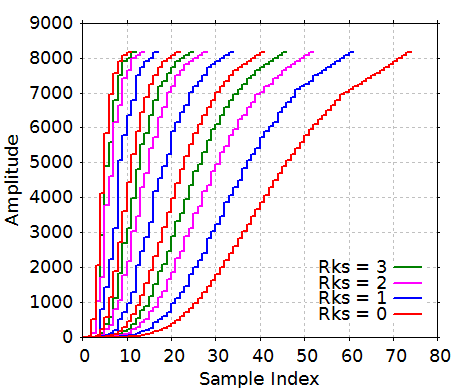

この回路と等価な処理を行うプログラムで、RATEの下位 2 ビットを 0 〜 3、RATE の上位 4 ビットの値を 12 から 15 まで変化させた場合 (ハイ・レート領域) のアタック・カーブを求めてプロットしたものを下に示します。