FPGA 版 FM 音源 (34) -- TX7 (OPS) 測定 (1)

今回は、どこのご家庭にもある TX7 のオーディオ出力を S/PDIF でキャプチャできるようにする改造の話です。

といっても、まだ初期の段階です。

TX7 は、 DX7 の音源部のみを取り出したものに相当し、YM2128 (OPS: Operator Type-S) と YM2129 (EGS: Envelope Generator Type-S) の組み合わせで 6 オペレータ FM 音源 (同時発音数 16) を実現しています。

「マルチティンバー音源」ではないので、16 音すべてが同じ音色となります。

9.4265 MHz の源発振を 2 分周した 4.71325 MHz をクロックとして、6 × 16 = 96 オペレータ分の処理を行い、サンプリング周波数 49.097 kHz でオーディオ出力します。

48 kHz S/PDIF にデータを乗せるには、源発振を 48 kHz × 192 = 9.216 MHz にすればよく、これは入手が容易な一般的な周波数なので、水晶振動子を換装すれば周波数の問題は解決できます。

TX7 では、電源基板、パネルスイッチ基板、コントロール・マイコン基板などの複数の基板に分かれており、FM 音源 IC およびアナログ回路は「AS シート」と呼ばれる基板に搭載されています。

改造前の AS シート (の一部) の写真を下に示します。

実はこの写真は「捏造」で、本当の改造前の写真をとり忘れたので DAC IC などを取り外した後の段階で、外した IC を (ハンダ付けせずに) 元の位置に戻して撮影したものです。

中央の紫色のセラミック・パッケージでピンが「千鳥の足跡」状の配列になっているのが YM2128 (OPS) で、その右側の黒いプラスチック・パッケージの IC が YM2129 (EGS) です。

手前中央やや右の 20 ピンの IC が 12 ビット・パラレル入力の BA9221 (ROHM) です。

OPS からのサウンド出力は、仮数部 12 ビット、指数部 2 ビット相当の浮動小数点相当のフォーマットで出力されてきます。

指数部については「デコード」された形で出力されており、SF0 〜 SF3 の 4 本の信号で仮数部を右シフトすべき量 0/1/2/3 ビットを表わしています。

SF0 〜 SF3 およびサンプリング・タイミングを表す SH1、SH2 は高耐圧オープンコレクタ・バッファ 7417 に配線されています。

S/PDIF インターフェースのためのサブ基板に、これらの信号を接続する方法として、仮数の 12 ビットが配線されている DAC と、SF0 〜 SF3,SH1,SH2 が配線されている 7417 を基板から外し、代わりに IC ソケットを装着することにより、サブ基板と接続することにしました。

しかし、背の高い電解コンデンサや、茶色い円板型の (積層でない) セラミック・コンデンサなどが邪魔になります。

そこで、立っている部品を寝かせる改造をしたのが下の写真です。

この際、思い切ってセラミック・コンデンサはすべて積層セラミック・コンデンサに換装する...ようなことはせず、スペース的に無理な 3 個以外は元のセラミック・コンデンサを寝かせて取り付けました。

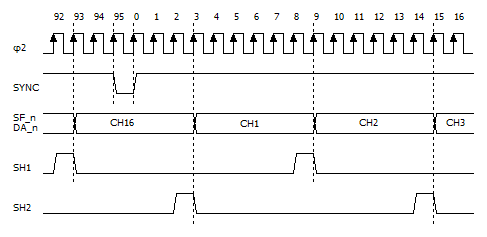

ネットを検索して見つかる DX7 サービス・マニュアルや TX7 サービス・マニュアルに記述されている情報、および実際に信号をオシロで観測した結果を元に書いたタイミング・ダイアグラムを下に示します。

OPS / EGS は 2 相のノンオーバーラップ・クロック φ1、φ2 で駆動されていますが、タイミングの基準は φ2 の立ち上がりのようです。

「SYNC」は OPS と EGS の同期を取るための信号で、サンプリング周期 (20.368 μs) に 1 回、φ2 クロック 1 個分のパルス幅で OPS から EGS に向けて出力されます。

SYNC が立ち下がるサイクルの次のクロック・サイクルを「0」として、仮のクロック・インデクスを付けてあります。

同時発音数 16 に対応して、おのおの 1 音分が 6 クロック幅 (1.27 μs) で全 16 音分のディジタル・データ (SF0 〜 SF3、DA1 〜 DA11) が出力されます。

DA 出力部の構成によっては、16 音それぞれを独立して出力することも可能です。 (実際の DX7 / TX7 では単に全部をまとめて 1 出力にしている)

DAC の入力レートは 4.71325 MHz / 6 = 785.54 kHz となり、かなり高速のものが必要です。

BA9221 はスペック上はセトリング・タイムは 250 ns になっています。

ディジタル的に「ビット・パーフェクト」な結果を得るためには、ディジタルのまま 16 チャンネル分の加算を実行して 1 チャンネル出力にまとめなければなりません。 また、16 音分加算することによりデータ・ビット幅が 4 ビット増えて、合計で 4 + 15 = 19 ビット幅になります。

サンプル・ホールド・パルス SH1、SH2 は、DAC のトランジェントでの出力変動が落ち着いた時点でサンプル・ホールドして「グリッチ」を避けるためのもので、SH1、SH2 交互に 1 パルスずつ出し合い、それぞれは 2 音に 1 回のパルス出力となっています。

これは、おそらく、DAC を SH1 側専用と SH2 側専用との 2 組用意すれば、それぞれの入力レートを半減 (392.8 kHz) できるので、安価だけど遅い DAC が使えるようにするための配慮だと思われます。

実際に発音する音とチャンネル番号との対応は、ボイス・アサイナによって決定されるので、1 音しか発音しない場合に必ず CH1 出力が使われるわけではありません。

初期状態の後、初めて発音される音は CH1 で、2 番目の音は CH9, 以下 CH5, CH13, CH3, CH11, ... ,CH16となっていくようです。

ハード的には、特定チャンネルのデータだけをキャプチャするのが簡単で、その中でも SYNC 信号をタイミング信号として使って CH16 をキャプチャするのが最も簡単だと思われます。

その場合、音源への入力データとして特定チャンネルだけを狙うことはできないので、常に 16 音分のデータを入力して、いずれかのデータが有効になるように考慮する必要があります。