3.3 V ノイズジェネレータ (3)

今回からは、ホワイトノイズをピンクノイズに変換するための -3 dB/oct (-10 dB/dec) の周波数特性を持つフィルタについて扱います。

まずは、実例として、minimoog および moog のモジュラーシンセのピンクノイズフィルタ回路を取り上げます。

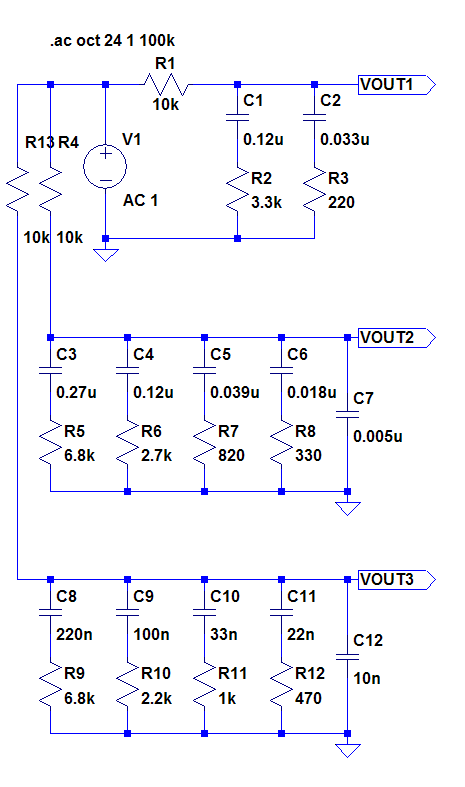

LTspice によるシミュレーション回路を下に示します。

「VOUT1」の回路が minimoog のもので、「VOUT2」の回路がモジュラーシンセのものです。

「VOUT3」の回路は、「VOUT2」の回路のコンデンサを E6 系列の手に入りやすい値に置き換え、抵抗値を E24 系列の中で調整したものです。

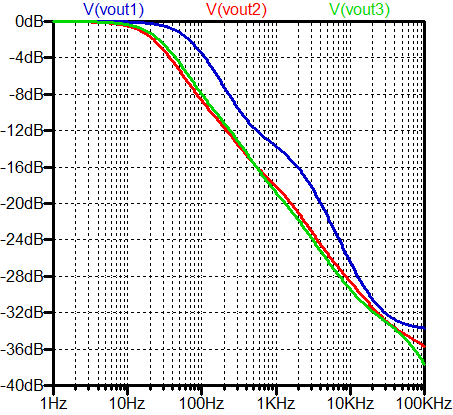

周波数特性のグラフを下に示します。

青色のグラフが minimoog のフィルタ特性で、赤色がモジュラーシンセの回路のもの、緑色がコンデンサの値を E6 系列にしたものです。

minimoog では、抵抗とコンデンサを直列にした「エレメント」が2つしかないので、特性がうねっていますが、モジュラーシンセの回路ではエレメントは4本に増えているので、より直線に近くなっています。

通常の 1 次 RC フィルタでは、カットオフ周波数以上の周波数では -6 dB/oct (-20 dB/oct) のスロープで振幅が減衰していきますが、これは、コンデンサの「積分要素」としての動作によるものです。

ピンクノイズ・フィルタに要求される特性が -3 dB/oct (-10 dB/dec) のスロープになるということは、2回作用させて1回の「積分」に相当するような「オペレータ」が必要になりますが、現実の素子でそのような特性のものは存在しないので、2個以上の素子を組み合わせて、近似的に実現することになります。

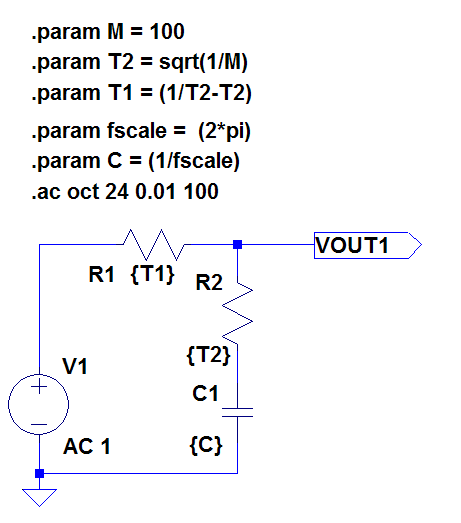

この目的で使われるのが、下の LTspice 用の回路図に示す「ラグ・リード・フィルタ」(lag lead filter) です。

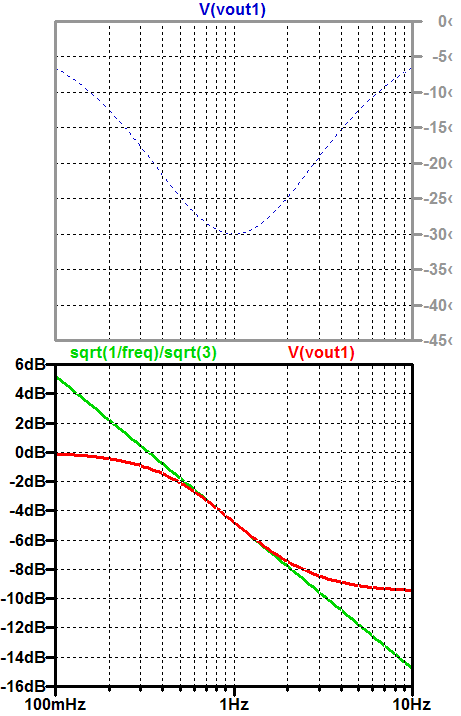

この回路での周波数特性を下に示します。

LTspice では角周波数 (rad/s) でのグラフ表示ができないので、本来は規準化角周波数で表示するべきですが、1 Hz を基準として表示するようにコンデンサの値を周波数スケーリングしてあります。 1 Hz を 1 rad/s だと思って見てください。

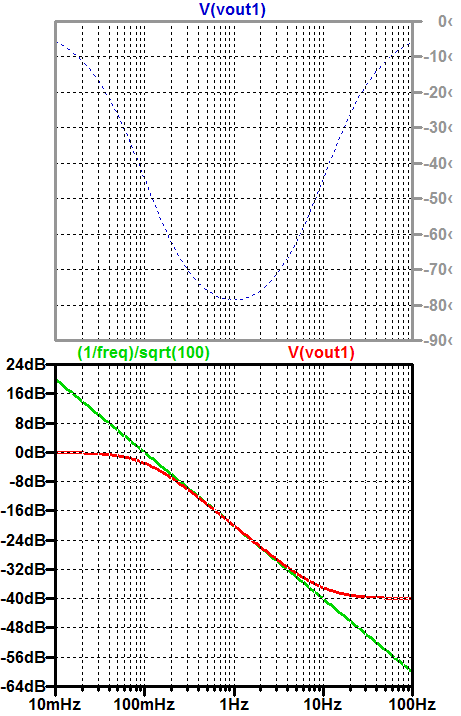

少し見にくいのですが、上のグラフで青色の破線で示されているのが位相特性で、低い周波数から出発して周波数が上がっていくと、いったん位相は遅れはじめますが、途中で持ち直して、逆に進みはじめて 0 °に戻っていきます。

位相が遅れて (lag) 進む (lead) 特徴から、「ラグ・リード・フィルタ」と呼ばれています。

振幅特性の方は、コンデンサが「オープン」と見なせるような低い周波数では、入力と出力が抵抗 R1 で結ばれているだけの状態となるので、信号の減衰はなく、ゲインは 0 dB になります。

これとは逆に、コンデンサが「ショート」と見なせるような高い周波数では、フィルタは R1 と R2 による単なる「分圧回路」となるので、振幅はゼロまで落ちずに一定値の R2 / (R1 + R2) となります。

そして、その中間の部分では、周波数と共にゲインが下がる特性となります。

R1 と R2 との比が大きい場合には、中間部のスロープは普通の1次フィルタと同じ -6 dB/oct (-10 dB/dec) となります。

上の回路の場合はこれに相当し、グラフ上で -6 dB/oct (-20 dB/dec) の直線を示す緑色の線と、フィルタの振幅特性の赤い色の線とが中央部で接していることが分かります。

振幅特性の低い周波数の「平坦部」から「遷移部」へ、また「遷移部」から高い周波数の「平坦部」への移り変わりの領域ではスロープが緩やかになっていますから、高低の「変曲部」が近接している状態では「遷移部」のスロープも -6 dB/oct (-20 dB/dec) よりも緩やかなスロープになることが予想されます。

下に、そのような条件での特性を示します。

振幅特性のグラフでの緑色の線が -3 dB/oct (-10 dB/dec) の直線を示しており、振幅特性の赤い線のグラフと中央部で接していることが分かります。

スロープが -3 dB/oct (-10 dB/dec) と見なせる範囲は狭いので、中心周波数をずらして構成したラグ・リード・フィルタを多段従続接続して広い周波数範囲に対応します。

この際、バッファをはさんで多段接続するのではなく、パッシブ回路で並列に接続したのが、最初に示した moog の回路のような形式です。

もちろん、パッシブ回路を直接接続するので、相互に影響し合い、フィルタの定数の設計は難しくなります。

下のリンク先の 2006 年 12 月 3 日の記事「-3 dB/oct の RC 回路」では、多数のエレメントを使用したパッシブ方式での設計例が示されています。

The Art of Analog Circuits

ラグリード 5 対で p-p リップルが 0.14 dB、ラグリード 8 対で p-p リップルが 0.018 dB という性能です。

実際にこの性能を得るためには、素子の値の精度が 5 桁とか 6 桁とかが必要になるので、できるだけ計算値に近い素子値を実現したうえで、さらに微調整が必要になるでしょう。

精度の良くない部品を使って可変部分を多くして、調整で合わせ込もうというアプローチでは収拾がつかなくなると思います。

次回は、ラグ・リード・フィルタ 1 段で -3 dB/oct (-10 dB/dec) のスロープを得る条件を求めてみます。