PSoC UDB 内 PLD/マクロセルによるアップダウン・カウンタ (5)

実際に 32 ビット・アダーのコンポーネントを作って、キャリー・チェインの中を下から上まで 32 段分キャリーが抜ける時間を測定してみました。

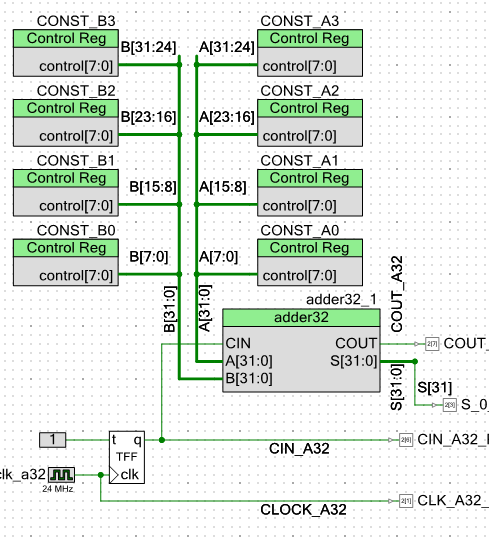

全体の回路図を下に示します。

「adder32」という名称になっているのが作成したコンポーネントで、CIN 入力 / COUT 出力を設けてあります。

入力 A / B 側それぞれに 8 ビットのコントロール・レジスタを 4 個配置して、任意の 32 ビット・データを供給できるようにしています。

これは、データ入力を定数値にすると、最適化でプロダクト・ターム (cpt0, cpt1) が定数の "0" あるいは "1" にまで簡単化されてしまい、本来の (A & B) や (~A & ~B) の形にならないためです。

「adder32」コンポーネントの Verilog 記述を下に示します。

//`#start header` -- edit after this line, do not edit this line // ======================================== // // Copyright YOUR COMPANY, THE YEAR // All Rights Reserved // UNPUBLISHED, LICENSED SOFTWARE. // // CONFIDENTIAL AND PROPRIETARY INFORMATION // WHICH IS THE PROPERTY OF your company. // // ======================================== `include "cypress.v" `include "lpm.v" //`#end` -- edit above this line, do not edit this line // Generated on 10/10/2016 at 01:31 // Component: adder32 module adder32 ( output COUT, output [31:0] S, input [31:0] A, input [31:0] B, input CIN ); parameter width = 32; //`#start body` -- edit after this line, do not edit this line // Your code goes here madd_sub #(.lpm_width(width+1), .lpm_direction(`LPM_ADD)) add32(.dataa({1'b0, A}), .datab({1'b0, B}), .cin(CIN), .result({COUT, S})); //`#end` -- edit above this line, do not edit this line endmodule //`#start footer` -- edit after this line, do not edit this line //`#end` -- edit above this line, do not edit this line

LPM (Library of Parameterized Modules) の madd_sub() を利用しており、COUT 出力は 1 ビット拡張方式で作っています。

入力 A / B の値を、CIN = 0 の場合、

- 加算結果が 0xFFFFFFFF になる

- 計算過程において各ビットから上位桁へのキャリーは出ない

という条件に選んでおきます。

たとえば、(A = 0xFFFFFFFF, B = 0x00000000) あるいは、(A = 0x55555555, B = 0xAAAAAAAA) などです。

これに CIN = 1 が加わると、LSB (b0) から MSB (b31) までキャリーが伝播していき、最終的に加算結果はゼロ (0x00000000) で、COUT = 1 となります。

回路では T-FF でクロックを分周して CIN = 0 と CIN = 1 の状態を交互に作りだしています。

使用マクロセル数は、adder32 で 32 + 2 = 34 マクロセル、T-FF に 1 マクロセルで、回路全体の合計では 35 マクロセルを使用しています。 マクロセルの消費分だけで言うと UDB (Universal Digital Block) 5 個分ですが、コントロール・レジスタを 8 個使っており、トータルでは 9 UDB を消費しています。

キャリー・チェインのマクロセルすべてがコントロール・レジスタが配置される UDB に同居していれば使用 UDB 数は 8 になるはずですが、配置の都合によりキャリー・チェインのみを含む UDB が 1 個あるため、トータル 9 個になっているようです。

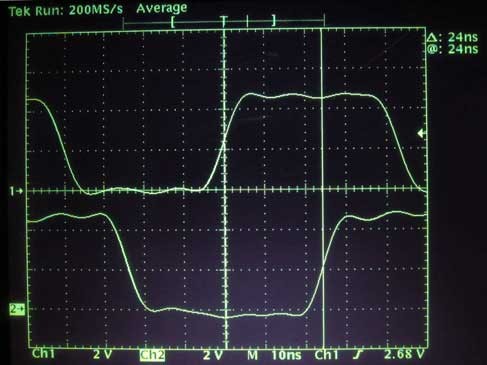

オシロで観測した CIN / COUT の波形を下に示します。

上のトレース (Ch. 1) が CIN で、下のトレース (Ch. 2) が COUT です。

使っているディジタル・オシロの帯域が 50 MHz で、立ち上がり時間は 7 ns 程度ですから正確な値ではありませんが、CIN の立ち上がりから COUT の立ち上がりまで、約 24 ns のディレイとなっています。