PSoC UDB 内 PLD/マクロセルによる乗算器

今回も PSoC3/4/5LP の UDB (Universal Digtal Block) 内の PLD/マクロセルによる回路の小ネタです。

LPM (Library of Parameterized Modules) ライブラリの「mmult()」コンポーネントによる乗算回路です。

mmult() は

result = (dataa * datab) + sum

の「積和演算」を計算するコンポーネントで、「sum」は省略可能で、その場合は単純な乗算器となります。

実際には、Verilog 組み込みの 2 項演算子「*」を使った場合の結果と同等のようです。

mmult() のパラメタ / 入出力ポートの定義を下に示します。

module mmult (dataa, datab, sum, result); parameter lpm_widtha = 1; parameter lpm_widthb = 1; parameter lpm_widths = 0; parameter lpm_widthp = 2; parameter lpm_representation = `LPM_UNSIGNED; parameter lpm_hint = `SPEED; input [lpm_widtha-1:0] dataa; input [lpm_widthb-1:0] datab; input [lpm_widths-1:0] sum; output [lpm_widthp-1:0] result;

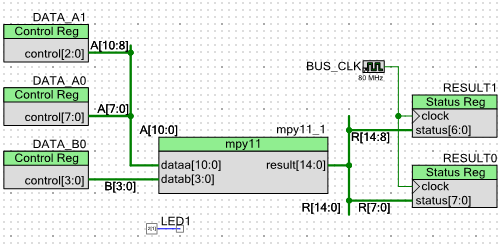

OPL3 のビブラート適用ずみの FNUMBER (11 ビット) に音色パラメタの「MULT」(4 ビット) を掛けることを想定して、11 ビット × 4 ビット乗算のコンポーネント「mpy11」を作成しました。 全体の回路を下に示します。

Verilog コードを下に示します。

//`#start header` -- edit after this line, do not edit this line // ======================================== // // Copyright YOUR COMPANY, THE YEAR // All Rights Reserved // UNPUBLISHED, LICENSED SOFTWARE. // // CONFIDENTIAL AND PROPRIETARY INFORMATION // WHICH IS THE PROPERTY OF your company. // // ======================================== `include "cypress.v" //`#end` -- edit above this line, do not edit this line // Generated on 10/19/2016 at 18:28 // Component: mpy11 module mpy11 ( output [14:0] result, input [10:0] dataa, input [3:0] datab ); parameter width_a = 11; parameter width_b = 4; parameter width_r = 15; //`#start body` -- edit after this line, do not edit this line // Your code goes here mmult #(.lpm_widtha(width_a), .lpm_widthb(width_b), .lpm_widthp(width_p)) mpy(.dataa(dataa), .datab(datab), .result(result)); //`#end` -- edit above this line, do not edit this line endmodule //`#start footer` -- edit after this line, do not edit this line //`#end` -- edit above this line, do not edit this line

dataa/datab/result のビット幅をパラメタで指定し、sum ポートなしで mmult() を呼び出しているだけです。

出来上がったモジュールでは、マクロセル 85 個を消費する、下図のような (Booth のアルゴリズム等を使用しない)「普通」の並列乗算器が生成されていました。

この図で、バス線に下から斜め 45° の線で接している表現はデータの LSB の下にゼロを補ってビット幅を増やすことを意味しています。 データを 1 ビットあるいは 2 ビット左シフトして、空いた位置に 1 ビットあるいは 2 ビットの「0」を詰めます。

同様に、上から斜め 45° の線で接している表現はデータの MSB の上に 1 ビットあるいは 2 ビットのゼロを付加してビット幅を増やすことを意味しています。

PSoC3/5LP の 24 UDB (192 マクロセル) におさまる範囲内で、どこまで被乗数、乗数のビット幅を増やせるかを試して見ました。

結果の表を下に示します。

| 8 ビット | 7 ビット | 6 ビット | |

|---|---|---|---|

| 16 ビット | × | × | 192 (100 %) |

| 15 ビット | × | × | 181 (94.3 %) |

| 14 ビット | × | × | 170 (88.5 %) |

| 13 ビット | × | × | 159 (82.8 %) |

| 12 ビット | × | 182 (94.8 %) | 148 (77.1 %) |

| 11 ビット | 189 (98.4 %) | 169 (88.0 %) | |

| 10 ビット | 174 (90.6 %) | ||

| 9 ビット | 159 (82.8 %) | ||

| 8 ビット | 144 (75.0 %) |

「×」となっている欄は 192 マクロセルにおさまらず、実現不可能なことを示しています。 空欄となっている組み合わせは、単に試していないだけです。

16 ビット × 6 ビットの組み合わせでは 192 マクロセルを消費し、100 % 使い切っています。

また、11 ビット × 8 ビットの組み合わせでは 189 マクロセルを消費し、98.4 % となっています。

短いほうのビット幅が 9 以上となる組み合わせでは全く実現不可能でした。