PSoC UDB 内 PLD/マクロセル キャリー・チェイン・コンポーネント

今回の小ネタは「cy_psoc3_carry()」モジュールの「ラッパー」となる「cy_p3_carry」コンポーネントです。

cy_psoc3_carry() モジュールは、arithmetic / carry-chain モードのマクロセル 1 個分なので、実際の複数ビットの加減算回路を構成するには複数個並べなくてはなりません。

その点からは、ビット幅を指定してモジュールを生成できる LPM (Library of Parameterized Modules) の madd_sub() モジュールを利用した方が実用的です。

cy_psoc3_carry() モジュールを直接使用する場合のメリットとしては、cpt0, cpt1 ポートに与える信号のロジック次第で加算/減算以外の機能を実現できることにあります。

しかし、3 項以上のプロダクト・タームを与えると、うまく合成できないようです。

実際のところ、加減算以外では「パリティ・チェック」程度の応用しかなく、それについても LPM では mparity() コンポーネントが用意されていて、5 入力以上の場合にキャリー・チェインを利用した回路が生成されます。

そんな訳で実用性は乏しいのですが、単なる「図」ではなく実際に動く回路として「原理的」な説明をする目的で、cy_proc3_carry() モジュールの呼び出しと 1 対 1 に対応する「ラッパー」としての cy_p3_carry() コンポーネントを作成してみました。

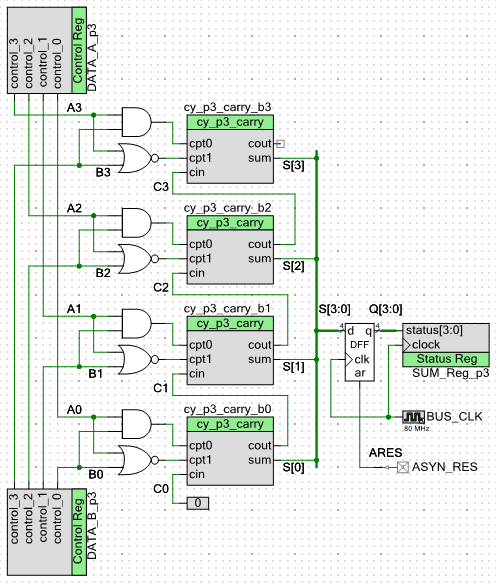

cy_p3_carry コンポーネントを利用して 4 ビット加算回路を実現したものを下に示します。

Verilog コード (cy_p3_carry.v) は下のようになっています。

//`#start header` -- edit after this line, do not edit this line // ======================================== // // Copyright YOUR COMPANY, THE YEAR // All Rights Reserved // UNPUBLISHED, LICENSED SOFTWARE. // // CONFIDENTIAL AND PROPRIETARY INFORMATION // WHICH IS THE PROPERTY OF your company. // // ======================================== `include "cypress.v" //`#end` -- edit above this line, do not edit this line // Generated on 10/18/2016 at 17:36 // Component: cy_p3_carry module cy_p3_carry ( output cout, output sum, input cin, input cpt0, input cpt1 ); //`#start body` -- edit after this line, do not edit this line // Your code goes here cy_psoc3_carry cc(.cin(cin), .cout(cout), .cpt0(cpt0), .cpt1(cpt1), .sum(sum)); //`#end` -- edit above this line, do not edit this line endmodule //`#start footer` -- edit after this line, do not edit this line //`#end` -- edit above this line, do not edit this line

そのまま cy_psoc3_carry() モジュールを呼び出しているだけです。

cy_p3_carry コンポーネントのシンボルでは cin 入力を下側に cout 出力を上側に描いているため、キャリー・チェインの伝播方向がこれまでの説明の図とは反対の、下から上への向きになっています。

cin には定数のゼロを接続し、また、cout 出力は使用していないので、cin マクロセルも cout マクロセルも挿入されず、マクロセル 4 個だけが生成されています。

上の回路図のコントロール・レジスタおよびステータス・レジスタを除く部分、つまり、

- AND ゲート 4 個

- NOR ゲート 4 個

- cy_p3_carry コンポーネント 4 個

- 非同期リセット付き D-FF 4 個

が UDB 1/2 個分、つまり PLD ひとつと、それに属するマクロセル 4 個で実現されています。