ADC 2 種 (PCM1808、TM7705N) の評価 (4)

TM7705N は 2 個購入して、そのうちの 1 個だけを測定していましたが、残りの 1 個について測定して見ると、セルフ・キャリブレーション後の残留オフセットが少なく、さらにディジタル・インターフェースの読み取りエラーの頻度は信号のドライブ能力に影響されにくいことが分かりました。 (ただし、エラーが皆無ではない)

そこで、測定は「良い」方のチップを対象として進めることにします。

AD7705 の英文データシートでは、

- 差動入力どうしをショートして GND に落とす (入力電圧 = 0 V)

- バイポーラ・モード

- 周囲温度 = 25 °C

- VDD = 5 [V]

- VREF = 2.5 [V]

- ゲイン = 128x

- 更新レート = 50 [Hz]

- サンプル数 = 1000

の設定にして測定した AD 出力値のグラフとして、 Figure 5. と Figure 8. が掲載されており、これらの図からノイズの評価をすることができます。 (日本語データシートでは 図2. と 図5.)

これらのグラフと比較するために、TM7705 を 5 V 電源で動作させて測定しました。

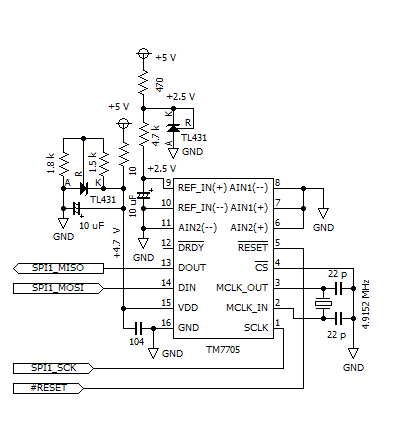

測定回路を下に示します。

5 V 電源は USB バスパワー由来のもので、安定化されていないので、 VDD としてはシャント・レギュレータにより 4.7 V 程度の電圧に安定化してから使用しています。

リファレンス電圧は TL431 の 2.5 V をそのまま使い、アナログ入力はすべてグラウンドに落として、測定対象のアナログ電圧としては常に「0 V」が入力されるようにしています。

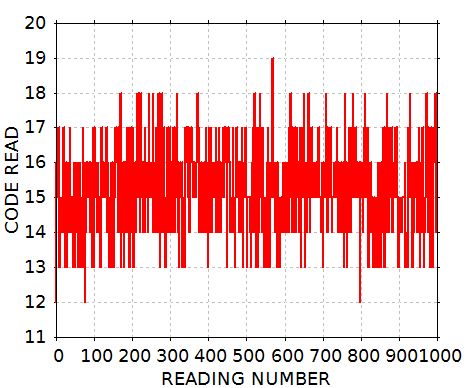

英文データシートの Figure 5. 相当のグラフを下に示します。

ただし、Figure 5. と違って、オフセット・バイナリを 2 の補数に変換して表示しています。

セルフ・キャリブレーション後に測定をしていますが、残留オフセットはゼロにはならず、1000 サンプルの平均で 15.2 となっています。

「悪い」チップの方では、セルフ・キャリブレーション後に残留オフセットが 30 程度となり、その後数十秒かけてゆっくり変化して最終的に 40 程度の値に落ち着きます。

ただし、AD 出力値のバラつき自体は良いチップと同等です。

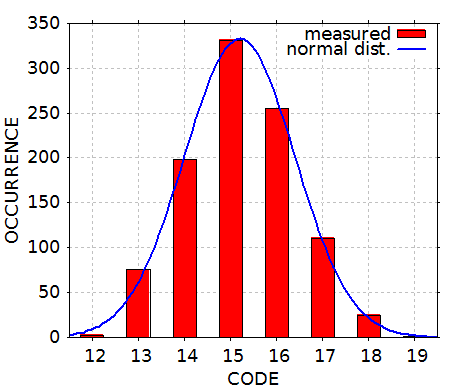

Figure 8. に相当するヒストグラムを下に示します。

赤色で塗りつぶされているバーが 1000 回測定したデータから作成したヒストグラムです。

データから計算した平均値 (μ = 15.2) と標準偏差 (σ = 1.2) をパラメタとして持つ正規分布の確率密度の曲線 (青色の線) も重ねて書いてあります。

正規分布の線はデータシートの Figure 8. にはありません。

この標準偏差 σ はノイズの rms 値に相当するので、1 LSB に相当する電圧

VREF [V] / (128 × 215) = 596 [nV/LSB]

と掛け合わせればノイズの rms 値が「電圧」として求まり、

1.2 [LSB] × 596 [nV/LSB] = 715 [nV]

となります。

英文データシートの Figure 5. では、「RMS NOISE = 600 nV」と記されているので、それより約 2 割大きいことになります。

ブレッド・ボード上の実験で条件が悪いことを考慮に入れると、TM7705 の (このサンプルでは) 残留オフセットが多いですが、ノイズ・レベルの性能は AD7705 と同等と言えると思います。