BBD コーラス (9) -- 逆数特性の VCO (4)

CE-2 / CE-3 の BBD クロック VCO 部の動作説明に移りますが、その前に、リセット型 VCO で逆数特性を得る方法について説明します。

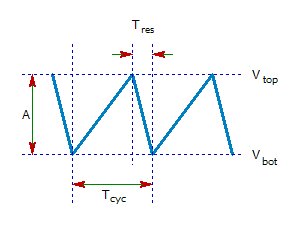

下に、リセット型 リニア VCO の出力波形 (のこぎり波) を模式的に表した図を示します。

回路の構成としては、入力電圧を電流に変換したものを、あるいは入力電流を直接に、タイミング・コンデンサに流して「積分」し、入力電圧に比例した傾きで直線状に変化する電圧を発生させます。

OP アンプを使った反転型積分器を使えば、入力電圧から電流への変換は抵抗 1 本ですみます。

単に、積分し続けるだけでは、電圧は無限に上昇することになりますから、出力波形の上限値 Vtop に達すると「リセット」を掛け、出力波形を下限値 Vbot まで低下させます。

このリセットに要する時間を Tres と表記します。

のこぎり波出力の振幅 A は、2つの電圧値、Vtop、Vbot で規定され、

A = Vtop - Vbot

ということになります。

出力波形の周期を Tcyc と表すと、入力電圧に依存する部分の時間は、

したがって、

となります。

ここで、リセット時間 Tres が入力電圧 Vin に依存せず、一定値であると仮定し、また、Vin も一定値であると仮定すると、(Vtop-Vbot) の直線変化に対して Tcyc も直線変化することが分かります。

リセット型リニア VCO では、リセット時間 Tres の存在そのものが誤差要因となりますが、逆数特性の VCO では、リセット時間の存在そのものは誤差要因とはならず、リセット時間の変動分が問題となります。

逆数特性の VCO では、VCO 入力として、Vtop、Vbot のいずれか、あるいは両方を変化させます。

リセット型 VCO の回路構成により、この 2 つの電圧は、コンパレータの比較電圧として使われている場合と、コンデンサの電圧をリセットするための (低インピーダンス) 電圧源として使われれている場合とがあります。

CE-2 / CE-3 の VCO の場合には、Vtop は CMOS インバータのスレシホールド電圧を利用していて、変化させるのが困難であり、VCO 入力としては使われていません。

したがって、リセット電圧値 Vbot を変化させて逆数特性を得ています。

もっと詳しく言うと、リセット期間では一定値にリセットしておき、それに続く積分期間の最初の比較的短い期間に、VCO 入力電圧に比例する電圧までクランプするようになっています。

次に、CE-2 / CE-3 の回路動作の説明に移りますが、まず、VCO としてではなく、固定周波数の発振回路として、VCO 全体の回路のおよそ 1/2 の部分の回路の説明をします。

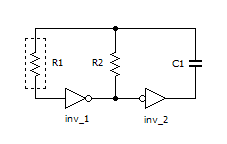

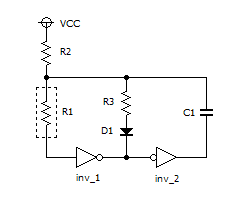

まず、CMOS インバータ 2 個で構成される典型的な発振回路を下に示します。

このタイプの回路は、MN3101 / MN3102 のデータシートにも「発振回路例」として記載されています。

図で点線で囲った R1 は、C1 と R2 が接続されている側 (これを「ホット側」と呼ぶことにします) の電圧が電源電圧範囲を超えて、CMOS 入力保護回路が作動することになるので、その電流を制限するためのものです。

タイミング・コンデンサ C1 の容量が小さい場合には、コンデンサに蓄えられる電荷の量も少なく、R1 なしで直結でも問題ありません。

MN3101 の場合には、データシートの表では、C1 = 22 pF, 100 pF, 200 pF の場合について、C1 = 22 pF であれば R1 = 0、つまり直結で、それ以外の C1 = 100 pF, 200 pF では R1 = 22 kΩ と記載されています。

MN3102 の場合には、データシート上では C = 22 pF, 100 pF, 200 pF の場合について、そもそも R1 に相当する抵抗は示されておらず、直結になっています。

発振周波数は (主に) C1、R2 で決まります。 R1 および CMOS 入力保護回路を流れる電流により発振周波数は影響を受けますが、R2 に比べて R1 の値が大きければ影響は少なくなります。

ただし、R1 の値があまり大きすぎると、インバータ 1 の入力部のストレー容量と R1 で形成される 1 次 RC フィルタの遅延時間が発振周波数に影響を及ぼしてきます。

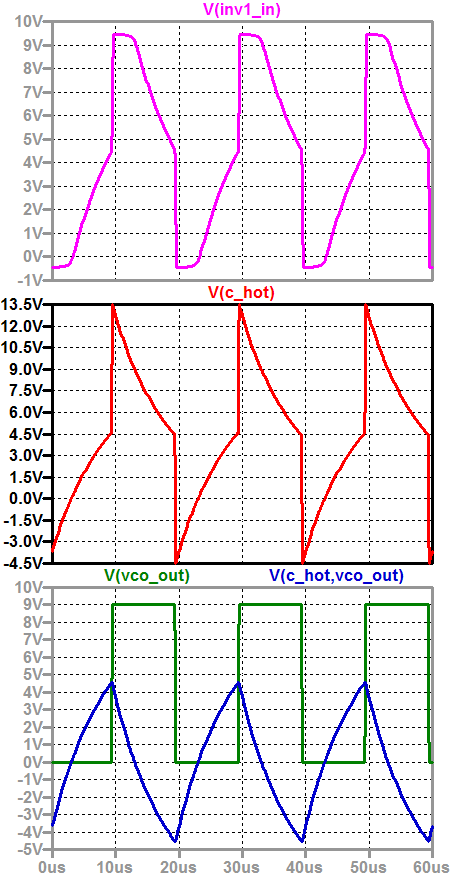

下に LTSpice でシミュレーションした各部の波形を示します。

CMOS インバータは、LTSpice 組み込みのロジック・インバータの Vhigh を 9 V に設定して他のパラメタはデフォルト値 (Vlow = 0 V、Vt = (Vhigh + Vlow)/2 = 4.5 V、遅延時間ゼロ、出力インピーダンス 1 Ω) としたものに、ダイオード 1N4148 を使用した電源レイルおよび GND レイルへの保護回路を組み合わせたものを使いました。

真ん中の段の赤色のトレースが C1 の「ホット側」の波形で、上の段のマゼンタ色のトレースがインバータ 1 の入力での波形で、下の段の緑色のトレースがインバータ 2 の出力、つまり C1 の「コールド側」の波形で、下の段の青色のトレースが C1 の「両端」の電位差の波形です。

回路定数は、発振周期が 20 μs 程度になるような値に選んであります。

真ん中の段の赤色のトレースの C1 のホット側の波形で説明すると、まず、最初の状態では、インバータの電圧レベルは、

inv1_in < 4.5 V

inv1_out = inv2_in = H = 9 V

inv2_out = L = 0 V

となっています。

インバータ 1 の出力は 9 V なので、

inv1_out → R2 → C1 のホット側 → C1 のコールド側 → inv2_out

という経路で「充電電流」が流れ、C1 のホット側の電圧が 1 次 RC 回路のステップ応答のエクスポネンシャル・カーブで上昇していきます。

電圧が上昇して、インバータ 1 のスレシホールド電圧 4.5 V を上回ると、インバータが反転し、

inv1_in >= 4.5 V

inv1_out = inv2_in = L = 0 V

inv2_out = H = 9 V

となります。

インバータ 2 の出力は C1 のコールド側に接続されているので、インバータ 2 の反転により、C1 のホット側の電圧は 9 V 分の「ゲタ」をはくことになり、

C1_hot = 4.5 V + 9 V = 13.5 V

まで急上昇します。

この時点で、インバータ 1 の出力は 0 V、インバータ 2 の出力は 9 V なので、

inv2_out → C1 のコールド側 → C1 のホット側 → R2 → inv1_out

という経路で「放電電流」が流れ、C1 のホット側の電圧が 1 次 RC 回路のステップ応答のエクスポネンシャル・カーブで下降していきます。

電圧が下降して、インバータ 1 のスレシホールド電圧 4.5 V を下回ると、再びインバータが反転し、

inv1_in <= 4.5 V

inv1_out = inv2_in = H = 9 V

inv2_out = L = 0 V

となります。

インバータ 2 の出力は C1 のコールド側に接続されているので、インバータ 2 の反転により、C1 のホット側の電圧から 9 V 分の「ゲタ」が外れ、

C1_hot = 4.5 V - 9 V = -4.5 V

まで急下降します。

これで、最初の状態に戻ることになり、あとはこの繰り返しで発振します。

インバータの特性が理想的ならば、完全にデューティー 50 % の方形波を発振することになりますが、実際には、そうはなりません。

それでも、デューティー 50 % に近い矩形波を発振する回路であることに変わりはありません。

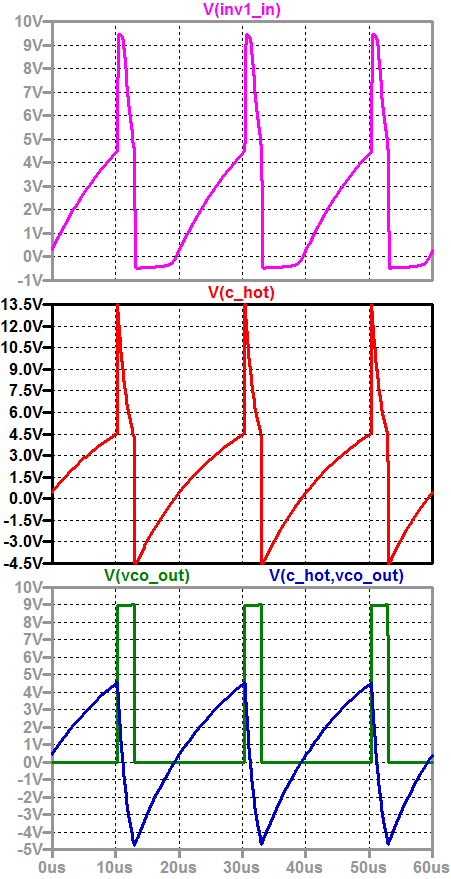

「充電電流」と「放電電流」の経路を変えて、デューティーの偏った波形を発振させる回路を下に示します。

「充電電流」は R2 を介して Vcc 側から、「放電電流」は R3、D1 を介してインバータ 1 出力から流す回路になっています。

「放電」時でも「充電電流」は休止しないので、「放電電流」の方を大きく設定しないと発振しません。

LTSpice シミュレーション結果を下に示します。

デューティーが 50 % から大きくずれていることが分かります。

R3 の値を小さくして放電電流を大きくしてやると、放電時間はさらに短くなり、「リセット型」の発振器の性質を持つようになります。

このとき、R2 に Vcc ではなく制御電圧を入力してやると、(リニアリティの悪い) リニア VCO として機能します。

この回路では、インバータ 1 の出力に「放電電流」を流すことを原因とする出力レベル変化が、次段のインバータ 2 入力のスレシホールド電圧を超えない必要があります。

データシートによれば、MN3101 では電源電圧 15 V でインバータ 1 の出力に 0.5 mA の電流を流した場合に 1 V 程度の電圧降下、MN3102 では電源電圧 5 V でインバータ 1 の出力に 0.4 mA の電流を流した場合に 1 V 程度の電圧降下があります。

インバータ出力から、あまり大電流を取り出せないので、CE-2 / CE-3 では、この回路形式は使われていないものと思われます。

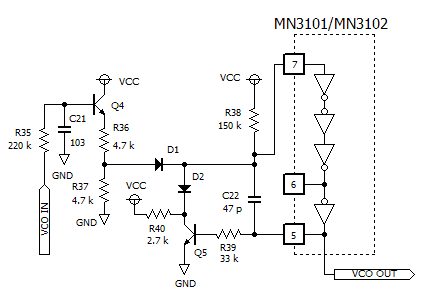

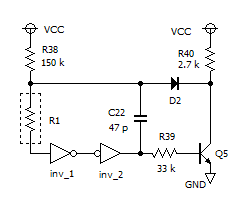

CE-2 / CE-3 の VCO 回路から、リセット型 (固定周波数) 発振器を構成する部分の回路を抜き出したものを下に示します。

実際の回路定数と、CE-2 での部品番号も示してあります。

放電電流を流すために NPN トランジスタ Q5 を設けています。

ロジック的には「インバータ」として機能しており、インバータ 2 の出力に接続されているので、ロジック・レベルとしては、インバータ 1 出力と同じ値となります。

R3 に相当する抵抗は省略されているので、放電電流を制限しているのはトランジスタの特性そのものになっています。

Q5 は P ランク (hFE = 200 〜 400) の 2SC945 が指定されており、hFE = 200 と仮定すると、ベース電流は、

Ib5 = (9 - Vbe5) / (33 [kΩ]) = (9 - 0.6) / 33e3 = 0.25 [mA]

であり、コレクタ電流は、

Ic5 = hFE5 * Ib5 = 200 * 0.25 [mA] = 50 [mA]

程度の値となります。

コレクタ負荷抵抗 R40 側に 3 mA 程度流れるので、差し引き最大 47 mA 程度の、ほぼ定電流が C22 の放電電流として流れることになります。

実際には、インバータ 2 出力に放電電流を流すことにより電圧降下が生じるので、電流値はもっと少なくなります。

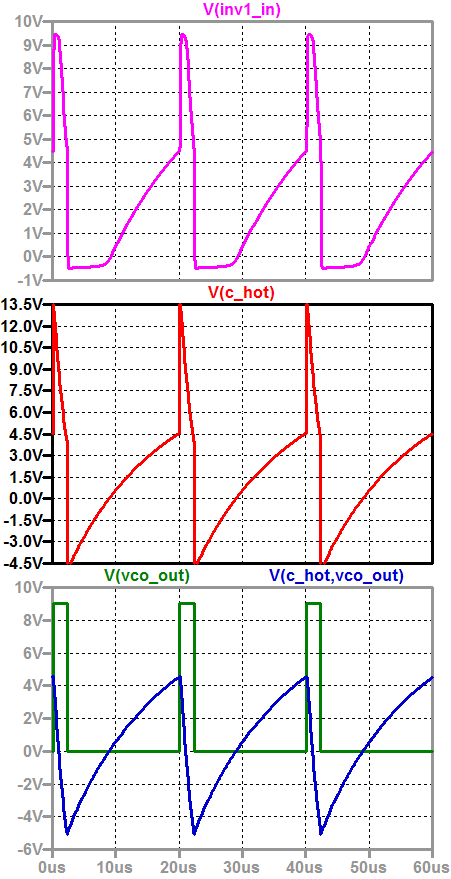

LTSpice でのシミュレーション結果を下に示します。

ただし、発振周期を 20 μs 程度にし、さらにリセット期間を見やすくするために、回路定数は実際の CE-2 のものとは変えてあります。 さらに R1 も挿入してあります。

インバータはデフォルトの出力インピーダンス 1 Ω のままで使っていて、苦もなく 60 mA 程度のピーク電流を供給できています。

リセット期間の C1 のホット側の電圧変化が直線に近く、Q5 が定電流源的に働いていることが分かります。

これで、下の CE-2 / CE-3 の回路図の D1 から右側の部分の回路の説明が済みました。

次回は、D1 から左側の部分の、VCO 入力電圧へのクランプ回路の説明に入りたいと思います。