PSoC5LP Prototyping Kit (10) --- DFB と Filter (2)

DFB (Digital Filter Block) では、BUS_CLK がクロック入力となるように決められていて、他の選択はできません。 BUS_CLK は CPU_CLK としても使われるので、CPU の動作スピードと同じスピードで DFB も動作することになります。

PSoC5LP Prototyping Kit 本体の CY8C5888LTI-LP087 では最大 80 MHz、KitProg 部分に使われている CY8C5868LTI-LP039 では最大 67 MHz となります。 DFB では、このクロック 1 サイクルで 24 ビット × 24 ビットの積和演算を行なうことができます。 (アキュムレータは 48 ビット)

何らかの理由で BUS_CLK を下げることが必要になった場合には、それに応じて DFB の処理能力も下がってしまうことになります。

出力信号としては、それぞれ 4 つの信号の中からひとつを選んで出力できるグローバル出力が 2 本と、割り込み出力 1 本と、DMA リクエスト出力 2 本との計 5 本しかありません。

データの入出力も、UDB (Universal Digital Block) などと直接に信号線を接続することはできず、データの受け渡しは DFB の内蔵レジスタに対して PHUB (Peripheral HUB) 経由で CPU / DMA からアクセスすることになります。

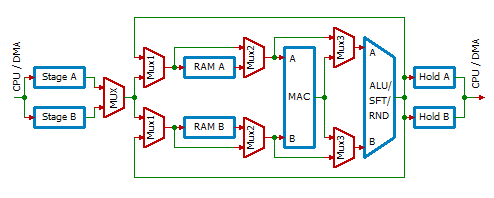

DFB のデータパス部分の簡略化したブロック図を下に示します。

フィルタ係数 / サンプル・メモリの RAM A / RAM B と、MAC (Multiply and ACcumulate unit) が心臓部です。 当然のことながら、乗算は「可換」なので、フィルタ係数とサンプル・データとが RAM A / B に分かれて収納されていれば良く、「フィルタ係数は RAM A に納めなければならない」といったような制約はありません。

図では RAM が FIFO のように表現されていますが、実際は ACU (Address Calculation Unit) のデータ・ポインタ・レジスタ (REG) を介した「間接アドレッシング」により、あらかじめ設定しておいた 16 個のアドレスまでは容易にランダム・アクセス可能です。

RAM のアクセス方法としては REG を ±1 あるいは FREG に設定した値だけインクリメント/デクリメントしたアドレスを対象にすることもできます。 このとき、MREG に設定した値でモジュロ演算してラップアラウンドさせることも可能です。

また、DFB を停止させれば CPU 側からは RAM にフルにランダム・アクセス可能になります。 PSoC Creator で生成されるプログラムでの DFB の初期設定時には、CPU 側から初期設定データを memcpy() 関数で一気に流し込んでいます。

RAM と MAC の周辺の 3 個のマルチプレクサ (MUX1 〜 MUX3) の設定により、積和演算結果をフィード・バックして計算することなども可能になっています。

MAC 出力には ALU / シフタ / ラウンダの機能ブロックが接続されており、積和演算結果と RAM 中のデータとの加減算 / 絶対値演算 / 飽和演算なども可能です。

シフタでは次の 8 通りのシフトが可能です。

- シフトなし

- 1, 2, 3, 4, 8 ビット右シフト

- 1, 2 ビット左シフト

「ラウンダ」では得られた 24 ビットの結果の下位 8 ビットを丸めて、上位 16 ビット分の結果に変換することができます。

上の図で Stage A / B とあるのがデータ入力レジスタで、Hold A / B とあるのがデータ出力レジスタですが、それらについては次回に説明します。