PSoC5LP Prototyping Kit (9) --- DFB と Filter (1)

今回からは PSoC5LP の DFB (Digital Filter Block) コンポーネントと Filter コンポーネントについての話題です。

DFB は UDB (Universal Digital Block) 上に実現されたファンクションではなく、「固定ファンクション」として実現されています。 PSoC5LP の一部の品種には内蔵されていませんが、内蔵されている品種でも 1 インスタンスだけであり、複数個を内蔵したものはありません。

PSoC5LP Prototyping Kit の KitProg 部に使われている CY8C5868LTI-LP039 にも内蔵されています。

DFB はその名の通り、主な用途はディジタル・フィルタですが、フィルタ専用ハードというわけではなく、小規模な「DSP」として構成されています。

DSP プログラム次第ではディジタル・フィルタ以外の用途にも使えますが、逆に、単純なディジタル・フィルタを実現する場合でも DSP プログラムが必要になってきます。

「DFB コンポーネント」を配置して、「カスタマイザ」を起動しても、ハードウェア的な設定項目はそれほど多くなく、DSP のアセンブリ言語を入力するエディタのタブがあるという「ガチ仕様」となっています。

手軽にディジタル・フィルタの機能だけを利用したいという場合には、「Filter コンポーネント」を使うことができます。

Filter コンポーネントでは、ディジタル・フィルタの実現に必要な DSP プログラムは自動で作ってくれて、ユーザは DSP プログラムには全く関わる必要がありません。

Filter コンポーネントのカスタマイザでは、機能は限定されていますが FIR / IIR ディジタル・フィルタの設計プログラムも含まれていて、フィルタのタップ数やフィルタ・タイプ、通過域端周波数、阻止域端周波数などを入力してフィルタ係数を求めることができます。

同時に周波数特性やステップ応答もグラフィカルに表示されるので、グラフを見て、十分満足の行く結果が得られるまでパラメタを変化させてやり直すことができます。

カスタム・フィルタ係数を読み込む機能もあるので、外部の (より高機能な) ディジタル・フィルタ設計プログラムを使って計算した結果を利用することもできます。

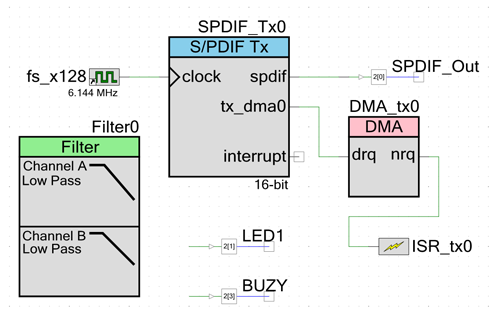

Filter コンポーネントと DMA と SPDIF_Tx を使って作った今回のプロジェクトのトップ回路図を下に示します。 このプロジェクトのファイルは公開を予定しています。

fs = 48 kHz の信号を 4 倍オーバーサンプリングして fs = 192 kHz の信号として送り出すことを想定しています。 この補間フィルタとして DFB の FIR ディジタル・フィルタを使います。

本来は PSoC4 で作成したシグマ・デルタ型 DAC コンポーネントで出力することを考えているのですが、まだ DMA 対応にはなっていないので、とりあえず SPDIF_Tx モジュールで出力するようにしています。

残念なことに、サンプリング周波数 96 kHz 以上に対応する SPDIF 入力機器を持っていないので、元のサンプリング周波数を 1/4 に落として 12 kHz とすることにより、4 倍オーバーサンプリング後の周波数を 48 kHz に据え置いてテストしています。

実際のところ、4 倍オーバーサンプリング周波数を本来の 192 kHz まで上げて処理が間に合っているかどうかを見ると、惜しいところで間に合っていない感じになっています。

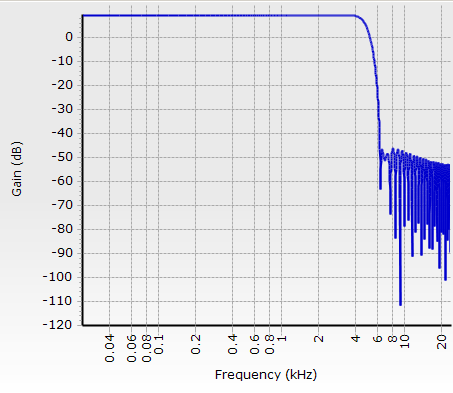

Filter コンポーネントのカスタマイザで設定した 63 タップ FIR フィルタの特性を下に示します。 (窓関数は Hamming、通過域端周波数 5 kHz、DC ゲイン +9 dB)

フィルタの係数メモリは 128 個あるのですが、ステレオ 2 ch で分け合うので、FIR フィルタでは 片 ch あたり最大 64 タップとなります。 タップ数が少ないので、4 倍オーバーサンプリング用補間フィルタとしては十分な特性ではありません。

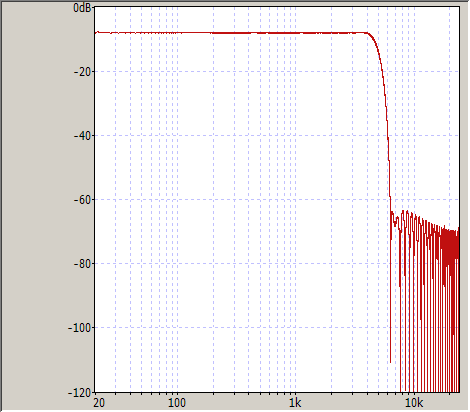

今回のプログラムでは、fs = 12 kHz で最小周波数 10 Hz から最高周波数 6 kHz までのリニア周波数スイープの正弦波を発生させているので、WaveSpectra のピーク・ホールド・モードで観測すると、DFB の特性を外部から観測することができます。 下にその結果を示します。

ゲインの表示は合わせていませんが、周波数特性の形は設計時のものと良く一致しています。