PSoC5LP Prototyping Kit (2) --- SPDIF_Tx と DMA (1)

今回は PSoC5LP の SPDIF_Tx コンポーネントと DMA モジュールについて取り上げます。

SPDIF_Tx コンポーネントは UDB (Universal Digital Block) 約 4 個分を費やして実現されており、次のような仕様となっています。

- サンプリング周波数の 128 倍のクロックを入力

- サンプリング周波数は最大 192 kHz まで

- リニア PCM フォーマットの 8 / 16 / 24 ビット・データに対応

- チャネル・ステータス・データを自動で読み込むモード (DMA マネージド・モード)、あるいは全てユーザが管理するモードのいずれかが選べる

- オーディオ・サンプル / チャネル・ステータス・データはバイト (8 ビット) 幅の DMA で転送される

- オーディオ・サンプルは L / R チャネルがインターリーブされた形で DMA 1 チャネルを使用するモードと、L / R チャネル独立で DMA 2 チャネル使うモードとが選択できる

UDB 内の FIFO にオーディオ・データを書き込めれば良いので、必ずしも DMA ではなく割り込みによるソフトウェア転送も可能ですが、8 ビット幅の転送に限られているので、48 kHz / 16 bit でも割り込みのレートは 192 kHz となり、その場合あまり実用的とは言えません。

DMA マネージド・モードにすればチャネル・ステータス・データの読み込みを自動でやってくれますが、暗黙のうちにリソースとして DMA 2 チャネルと割り込み 2 本を消費します。

したがって、特別な事情がない限り、オーディオ・データの転送は DMA で行なうのが普通となります。

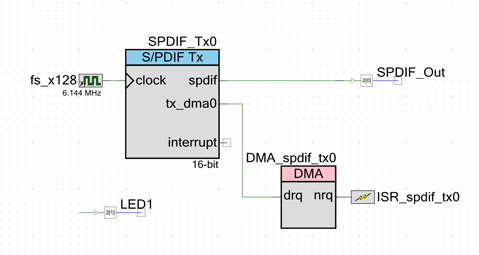

今回作成したプロジェクトのトップ・レベルの回路を下に示します。

48 kHz のサンプリング周波数に対して、その 128 倍の 6.144 MHz クロックを SPDIF_Tx コンポーネントに供給しています。

オーディオ・データ L/R 交互のモードを選んだので、DMA および割り込みをひとつずつ使用します。

SPDIF_Tx コンポーネントには、あらかじめ出力ピンとして「SPDIF_Out」が定義されており、リソース・マネジャーの「Pins」画面で実際のピンを割り当てるだけで出力可能となります。

今回、出力するオーディオ信号は、毎度おなじみ DDA (Digital Differential Analyzer) アルゴリズムでソフトウェア的に発生させたサイン波、コサイン波を使うので、「ハードウェア」的な設定としては上の回路だけです。

DMA の設定のためのプログラムについては、DMA コンポーネントのカスタマイザで行なうのではなく、PSoC Creator の Tools メニューから実行できる「DMA Wizard」を利用して作成します。 詳しくは後述します。

ビルド後のリポート・ファイル (.rpt) の論理合成結果のサマリを見ると、

---------------------------------------------------------

Technology mapping summary

---------------------------------------------------------

Resource Type : Used : Free : Max : % Used

=========================================================

UDB Macrocells : 23 : 169 : 192 : 11.98%

UDB Unique Pterms : 62 : 322 : 384 : 16.15%

UDB Total Pterms : 66 : : :

UDB Datapath Cells : 4 : 20 : 24 : 16.67%

UDB Status Cells : 1 : 23 : 24 : 4.17%

StatusI Registers : 1

UDB Control Cells : 2 : 22 : 24 : 8.33%

Control Registers : 1

Count7 Cells : 1 のようになっています。

PSoC5LP では UDB 24 個ですから、使用率 16.67 % 以下であれば UDB が 4 個しかない PSoC 42xx シリーズでも原理的には実現可能ということになります。

もっとも、PSoC4 シリーズでは DMA がないので実現できたとしても、実用性はありません。

「UDB Total Pterms」の項が「66」と、UDB 4 個分の「64」を超えているので、わずかに UDB 4 個分をハミ出しているのかも知れません。

また、PSoC Creator 3.0 SP2 でビルドした後の STA (Static Timing Analysis) の結果を見ると、

- Register to Register Section

- Setup Subsection

- Source Clock : CyBUS_CLK : Positive edge(Required Frequency 49.152 MHz)

- Destination Clock : CyBUS_CLK : Positive edge(Required Frequency 49.152 MHz)

Path Delay Requirement : 20.3451ns(49.152 MHz)

Source Destination FMax

(MHz)Delay

(ns)Slack

(ns)\SPDIF_Tx0:

bSPDIF_Tx:

AudioTx:

u0\

/f0_bus_stat_combDMA_spdif_tx0

/dmareq54.678 18.289 2.056 \SPDIF_Tx0:

bSPDIF_Tx:

ChStatusGen:

u0\

/f0_bus_stat_comb\SPDIF_Tx0:

Cst0_DMA\

/dmareq61.732 16.199 4.146 \SPDIF_Tx0:

bSPDIF_Tx:

ChStatusGen:

u0\

/f1_bus_stat_comb\SPDIF_Tx0:

Cst1_DMA\

/dmareq69.089 14.474 5.871

と、BUS_CLK (= CPU_CLK) の Fmax の最小値が約 55 MHz となっていることが分かります。

この状態では CPU クロックを約 55 MHz 以上に上げると SPDIF_Tx コンポーネントの中でタイミング・バイオレーションが起こる可能性があり、PSoC5LP Prototyping Kit のターゲット CPU CY8C5888LTI-LP097 の CPU クロックの上限の 80 MHz まで BUS_CLK = CPU_CLK を上げげられないことになります。

今回のプロジェクトでは CPU のスピードは必要とされないので、外付け水晶振動子の 12.288 MHz を PLL で 4 倍にした 49.152 MHz を BUS_CLK = CPU_CLK として使っています。

同じプロジェクトを PSoC Creator 3.3 でビルドすると、SPDIF_Tx のバージョンは V1.20 で変化ないのですが、Fmax は約 65 MHz になるので、実際に「配置」される位置によりディレイ量が変化するものと思われます。

次回は DMA について触れます。