STM8S-Discovery (10)

3 月 16 日付けの記事で、「ジッタが乗ることもなく」と書きましたが、これは実際にジッタの量を定量的に測定してみた結果と言うわけではありません。

マイコン - DAC 間のシリアル・データ・インターフェース信号には大きなジッタが乗っているのに、オーディオ出力信号にはジッタが感じられないので、シリアル信号のジッタへの寄与は「ゼロ」と見なしました。

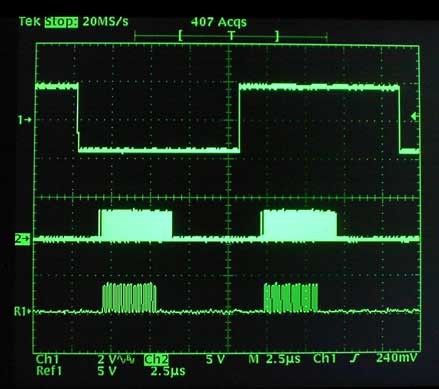

まず、シリアル・クロックの波形写真を下に示します。

一番上のトレースが LRCK で、一番下のトレースがメモリに記憶しておいた SCK です。

これが 16 ビット分のクロックの本来の幅です。

真ん中のトレースは、エンベロープ蓄積モードで表示した SCK で、べったりと塗りつぶされた範囲で SCK のタイミングが変動していることを示しています。

つまり、下のトレースの本来のクロックの幅と比較すると、ハミ出ている分のジッタが存在していることを表しています。

このジッタが、そのまま出力オーディオ信号に現れれば、相当大きなジッタの影響を感じるはずですが、再生音からは感じられないので、出力にジッタは乗っていないと判断しています。

また、BU9480F では、データシートに

Interpolation and original data output are timed respectively to the leading edge and leading edge of LRCK, and so LRCK should be set to a duty of 50%.

という記述があり、オリジナル・データ (と補間データ) は LRCK のエッジのタイミングでアナログ出力されることが明記されています。

LRCK は CPU クロックからハードウェア・タイマを使って生成しているので、ソフトウェアが介入しないのでジッタはなく、LRCK に同期して出力される BU9480F のアナログ信号にもジッタは乗らないことになります。

これは以前の記事 (→こちら) でも実験により確かめてあります。

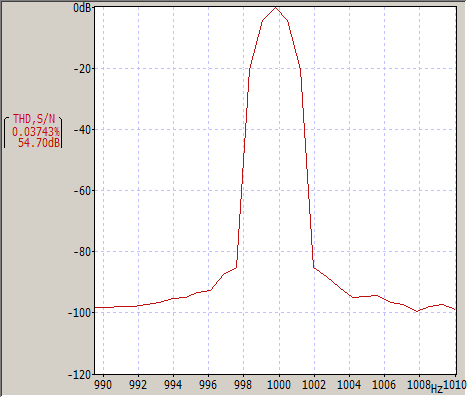

この「ジッタの乗らない」BU9480F での 1 kHz サイン波出力の「メインローブ」付近を拡大して観測したのが下の図です。

ほぼ Blackmann 窓のメインローブの形状そのもので、ジッタによるスプリアスは見られません。

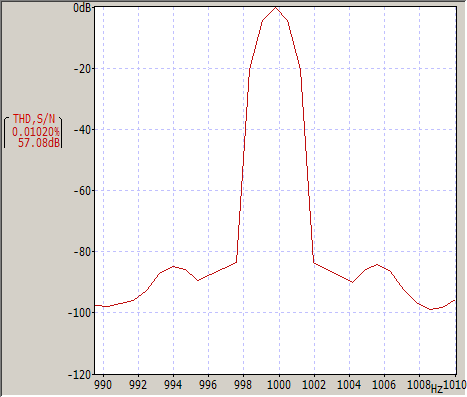

同様に、PCM1716E の場合のメインローブを次に示します。

これは BU9480F の場合とほぼ同じであり、このことからも「ジッタはない」と結論づけられます。