LPC2388 マイコン基板 (3)

今回は、LPC2388 の I2S モジュールの出力を標準フォーマットの DAC に接続するための回路を考えます。

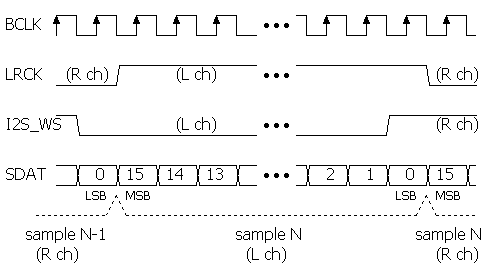

まず、I2S フォーマットと標準フォーマットの信号のタイミング・チャートを示します。

まず、シリアルデータ入力の基準となるクロックがビットクロック BCLK で、「シリアルクロック」という場合もありますが、ここでは「BCLK」と表記することにします。

この BCLK の立ち上がりエッジでシリアルデータ SDAT や LRCK (WS) を取り込みます。 シリアルデータとしての「ビット同期」は、この段階で確立します。

クロック・エッジでデータを取り込むので、正しくデータを読むために、DAC 側では BCLK の立ち上がりエッジに対して「セットアップ・タイム」と「ホールド・タイム」が規定されているのが普通です。

そのセットアップとホールドのマージンを最大にするために、送り出し側では SDAT、LRCK、WS の信号は、クロック周期の半分、すなわち、クロックの立ち下がりエッジで変化させるようになっています。

BCLK と SDAT については、I2S フォーマットと標準フォーマットとの間に差はないので、何の変更も加えず、I2S 出力から DAC へ直結できます。

ただし、DAC を 5V 電源で動作させている場合、スペック上では「H」レベルの最小値は Vdd の 70% の 3.5V になっていますから、3.3V 電源のマイコンの出力では、ワーストケースではスペックを満たさないことになります。

実用上は問題ないと思いますが、気になる場合は、3.3V → 5V へのレベル変換のバッファを使用するか、DAC も 3.3V 電源にすると良いと思います。

私の場合は、V850 用のベースボードをそのまま利用しているので、周辺回路は 5V 電源での動作です。

16 ビット・ワードの区切りや、L/R ch の区別のための信号が、I2S では WS (Word Select) で、標準フォーマットでは LRCK (L/R clock) です。 このふたつの信号には、違いがあるので、変換を施す必要があります。

その違いをあげてみると、

- 標準フォーマットでは、ひとつの 16 ビット・ワードの LSB (b0) と、次の 16 ビット・ワードの MSB (b15) の間で LRCK が変化する

- I2S フォーマットでは、ひとつの 16 ビット・ワードの b1 と b0 の間で WS が変化する

- 標準フォーマットでは LRCK=1 で転送されるデータが L ch、LRCK=0 で転送されるデータが R ch

- I2S フォーマットでは WS=0 で転送されるデータが L ch、WS = 1 で転送されるデータが R ch

となります。

L/R の定義が逆になっている点については、論理値を反転すればよく、タイミングの違いについては、WS を BCLK ひとつ分遅らせれば LRCK と同じになります。

これが標準フォーマットから I2S への変換だと、15 クロック分遅らせる必要があるので回路が大きくなります。

まず、動作が確実な回路を下に示します。

まず、1段目のポジティブ・エッジ・トリガの D-FF (74HC74) で I2S の WS をラッチします。 BCLK の立ち上がりでラッチしているので、セットアップ/ホールドのマージンは最大で、クロックが高速の場合でも問題ありません。

2 段目の D-FF のクロック入力はインバータ1段で反転しているので、実効的にネガティブ・エッジ・トリガとなります。 したがって、2 段目の出力が変化するのは BCLK の立ち下がりの付近となり、接続されている DAC にとってもセットアップ/ホールドのマージンは最大になります。

次は、なるべく回路が簡単になるように考えます。

まず、WS を1クロック遅らせるのは、ネガティブ・エッジ・トリガの D-FF があればできますし、論理値の反転は、その D-FF に反転出力があればすむ話です。

つまり、

- 反転出力を持つ

- ネガティブ・エッジ・トリガの

- D-FF

があれば、その D-FF ひとつで実現できます。

しかし、残念なことに、容易に入手可能な 74HC シリーズのロジック IC には、このようなデバイスはありません。 ネガティブ・エッジ・トリガの FF は JK-FF のタイプが多く、D-FF のタイプはありません。

数少ないネガティブ・エッジ・トリガのデバイスと、インバータを組み合わせたのが次の回路です。

3 月 30 日付けの記事では、DAC に LRCK 信号の極性切り替えが可能な μPD6376 を使い、インバータを省略して 74HC298 ひとつの回路を使用しています。

その回路での波形写真を下に示します。

信号は、上から、それぞれ、I2STX_CLK、I2STX_WS、LRCK、I2STX_SDA です。

2 現象のディジタル・オシロを使用しており、リアルタイムで観測しているのは、真ん中の 2 本のトレースで、上下のトレースはメモリに記憶させておいた波形です。

インバータがない回路なので、LRCK の波形は本来必要なものとは反転している形になります。

I2STX_WS の立ち上がり付近を拡大したものを下に示します。

LRCK が I2STX_WS に対して1クロック遅れていることが分かります。

一番下のトレースを μPD6376 のアナログ出力に変えて、その変化するタイミングを見たのが次の写真です。

データシート通り、LRCK のエッジから 4.5 クロック後にアナログ出力が変化しているのが分かります。

この回路の問題点としては、WS 信号と BCLK 信号とのタイミング関係のスペックが明示されていないので、ホールド・タイムが不足する可能性があることです。

そのため、インバータを FF のデータ入力側に付け、少しでもホールド・タイムを確保するようにしています。

次は、LRCK 信号を立ち下がりエッジ側で変化させることをあきらめ、DAC 側のスペックを満足させるようにして、立ち上がりエッジで動作する D-FF を使う方法です。

2 段目の FF は、フリップフロップとしての動作ではなく、ダイレクト・セット/ダイレクト・リセット端子を利用して、単なるバッファとして遅延時間だけを利用しています。

この回路での遅延時間が DAC にとってはホールド・タイムとなるわけですから、スピードは遅い方が良く、メタルゲート CMOS の 4013 を使えば 5V 電源でのディレイの標準値が 100 ns 程度とれます。

74HC74 を使った場合の実測値としては、BCLK のエッジから LRCK の変化までの遅延は約 25 ns で、μPD6376 のホールド・タイムの最小値 12 ns は満足していますが、BU9480F のホールド・タイムの最小値 60 ns は満足していません。

しかし、実際の回路では特に問題なく動いています。