PIC18F14K50 (7)

2 月 3 日付けの記事の回路の構成では、Franco の補償が効かないことが分かり、回路を変更しました。

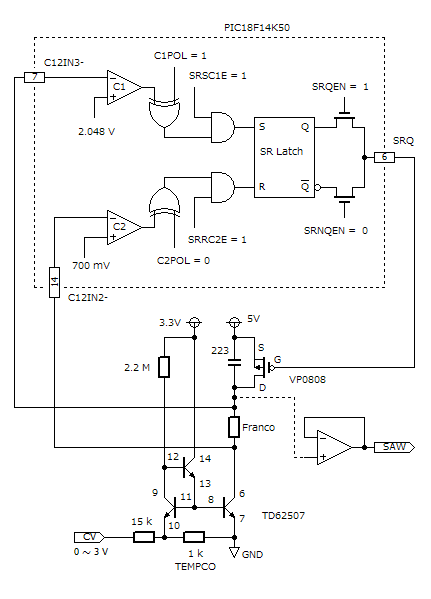

下に PIC18F14K50 内部のモジュールの構成と共に表示した回路図を示します。

前の回路では、2つのコンパレータ入力を一緒にして補償抵抗の一端に接続しているので、抵抗による電圧降下は両方のスレシホールドに等しく作用し、のこぎり波の振幅には変化が表れず、補償の効果がありません。

補償を有効にするためには、2つのコンパレータ入力を分離し、抵抗の両端に、ひとつずつ接続する必要があります。

別の構成の回路での実験も考慮し、コンパレータの入力ピンを「C12IN1-」(15 番ピン) から「C12IN2-」(14 番ピン) と「C12IN3-」(7 番ピン) とに変えました。

7 番ピンは LVP (低電圧プログラミング) の「PGM」入力になっていますから、コンフィグは「LVP OFF」にしておきます。 18F14K50 用の Microchip 製 HID ブートローダでは最初から「LVP OFF」になっています。

空きとなった「C12IN1-」は SR ラッチの「INT1」入力として使い、VCO のハード・シンク機能に利用する予定です。

現在はまだ、のこぎり波のバッファを実装していませんが、その入力の接続箇所を示してあります。

アンチログ出力側の抵抗の端子に接続すると、入力容量の影響で、のこぎり波上端近くの波形が悪くなります。

上の図のように、タイミング・コンデンサ側に接続すると、入力容量はタイミング・コンデンサに「吸収」される形となり、波形に影響を与えません。

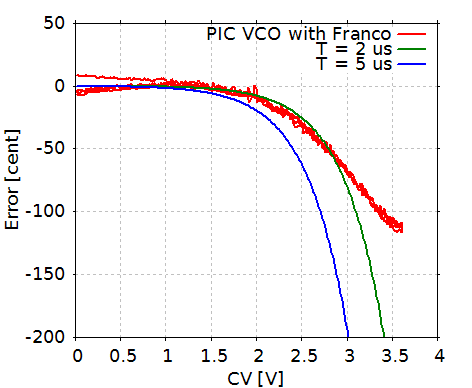

Franco の補償の抵抗として 220 Ω を使って測定した結果を下に示します。

赤の線が 4 回の連続測定結果を重ねてプロットしたものです。

青の線はリセット期間を 5 μs と仮定した場合の誤差の理論値で、補償なしの測定結果の代わりとしてプロットしています。

計算では補償抵抗値は 220 Ω でしたが、実際には、かなり改善されているが、少し補償値が足りないという結果になっています。

どのくらい足りないかを見積もるために、リセット期間 2 μs 相当の誤差のグラフもプロットしています。(緑の線)

追加の補償は 2 μs 相当あれば良さそうで、具体的には 330 Ω の抵抗と交換して、再度測定してみたいと思っています。