XR2206 (9)

XR2206 で、のこぎり波を発生させる場合の波形写真を示します。

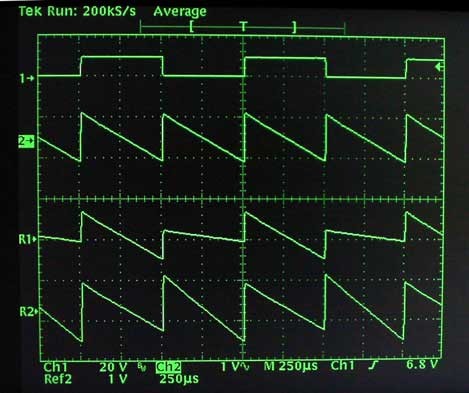

まず、VR3 を Vcc/2 側いっぱいに回して、3 番ピンのバイアスが一定の場合のランプ波形を下に示します。

1番上のトレースが方形波出力 (11 番ピン) で、2番目のトレースが VR1 / VR2 を正しく調整してランプ波形がそろっている場合の出力 (2 番ピン)、3番目、4番目は調整が正しくなくて、ランプ波形がそろっていない場合の波形です。

上のふたつの波形はリアルタイムで見ているものですが、下のふたつはメモリしておいたものです。

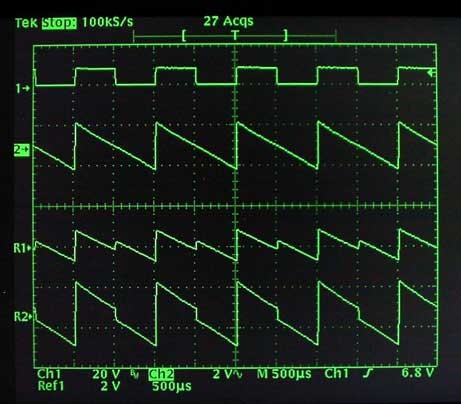

次の写真は、3 番ピンに方形波によるオフセットを加えて、のこぎり波を合成した場合の波形です。

1番上のトレースが方形波出力 (11 番ピン) で、2番目のトレースが VR3 を正しく調整して、のこぎり波がうまくつながった場合の出力 (2 番ピン)、3番目はオフセットの量が不足している場合、4番目はオフセット量が多すぎる場合の波形です。

のこぎり波を波形の合成によって得ているので、当然のことながら、グリッチが生じます。

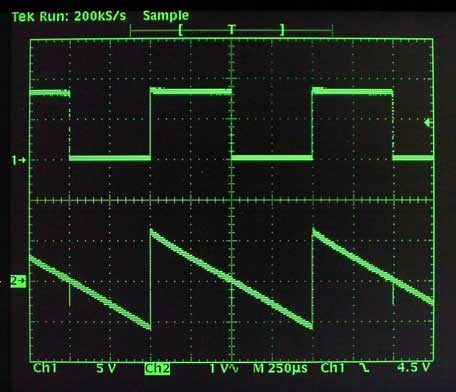

上の写真ではオシロの「アベレージ機能」で平均化して表示しているのでグリッチは見えませんが、「ドット蓄積モード」で表示したのが下の写真です。

上の波形は方形波出力 (11 番ピン) で、下の波形は 2 番ピンの出力です。

真ん中の波形は垂直軸と重なっていて分かりませんが、左右の波形では、のこぎり波の中央部、方形波の立ち下がりの位置に下向きのグリッチが乗っているのが分かります。

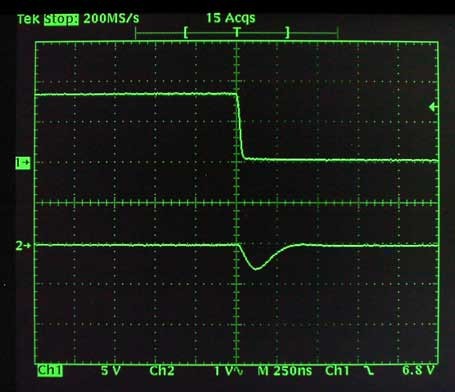

そのグリッチ部分を拡大したのが下の波形写真です。

パルス幅は 300 ns 程度、レベルは 0.6 V 程度です。

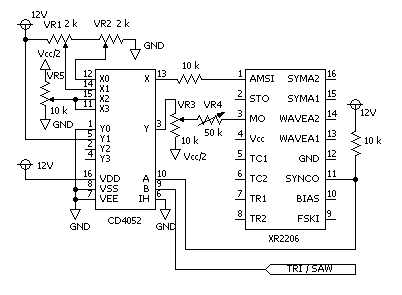

4-to-1 アナログ・マルチプレクサの CD4052 を使って、のこぎり波と三角波を切り換えられるようにした回路を次に示します。

前の回路に比べて VR5 が追加されていますが、これは三角波のレベル調整用です。

この回路では、のこぎり波と三角波の DC レベルを独立に調整できません。

Vcc が 12 V ですから、耐圧 18 V のメタルゲート CMOS の 4052 を使う必要があります。

シリコンゲート CMOS の 74HC シリーズの 74HC4052 では、Vdd = 12 V、Vee = 0 V、Vss = 6 V として、ロジックレベルを 6 V 〜 12 V とすれば使えないことはありませんが、スペックぎりぎりの状態となります。

この回路は、まだ実際に試してはいません。