PSoC5LP Prototyping Kit (12) --- DFB と Filter (4)

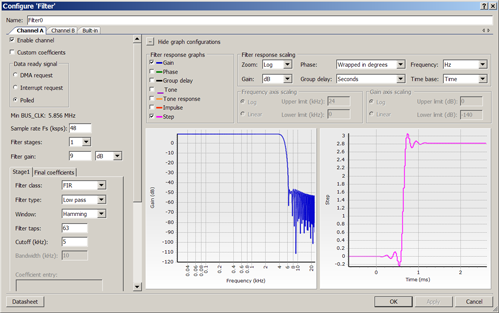

Filter コンポーネントを回路図上に配置して、コンポーネントをダブル・クリックして開くカスタマイザ (設定ダイアログ) の画面を下に示します。 (画像をクリックすると拡大します)

Filter コンポーネントがサポートしている 2 チャネルに対応して、チャネル A と、チャネル B との 2 つの設定タブがあります。 上の図はチャネル A に対するものです。

左側のペインにはフィルタの DMA / 割り込み出力の設定と、フィルタの仕様を入力する欄があります。

右側のペインには、得られたフィルタ係数から計算した周波数特性とステップ入力に対するトランジェント波形のグラフが表示されます。 (時間波形はインパルス応答の表示にも切り替えられる)

グラフの仕様を設定する部分を隠して、上下方向をフルにグラフ表示に使うこともできます。

各チャネルあたり最大 4 段のフィルタを縦続した構成とすることができます。 各段ごとに FIR (Finite Impulse Response) 直線位相フィルタ、あるいは IIR (Infinite Impulse Response) バイクアッド (biquad) フィルタのいずれかを選択することができます。

FIR の各段のフィルタ係数は「たたみ込まれて」ひとつの FIR フィルタ係数にまとめられます。

IIR バイクアッド・フィルタは、もともと 2 次セクションの縦続で実現されているので、IIR の各段はそのまま縦続されて、ひとつの IIR バイクアッド・フィルタにまとめられます。

実現できるフィルタの次数 (タップ数) としては、DFB のリソースすべてをひとつの FIR フィルタで使用する場合には最大 128 タップまで、IIR バイクアッド・フィルタでリソースを占有する場合については 50 次 (25 バイクアッド・セクション) までとなります。

2 チャネル使用する場合、および FIR、IIR 混在の場合には、この最大値をそれそれで分け合う形となります。

カスタマイザの左側のペインのフィルタ仕様入力部を拡大したものを下に示します。

「Enable channel」にチェックを入れると、そのチャネルが有効になります。 1 チャネルのみ使用する場合にはチャネル A、チャネル B のいずれかのみを有効とします。

「Custom coefficients」にチェックを入れると、Filter コンポーネントのフィルタ設計機能は使わず、外部のフィルタ設計ソフトなどで求めたフィルタ係数のみを利用するモードとなります。

ハードウェアの出力データ・レディ信号の設定としては、

- DMA request

- Interrupt request

- Polled

の 3 つのラジオ・ボタンの選択肢しかありません。

DMA リクエスト信号はチャネル A、B 独立の合計 2 本ですが、インタラプト出力は A / B 共通の 1 本です。

「Polled」を選ぶと、完全にソフトウェアによるレジスタ・アクセスのみとなり、Filter コンポーネントには全く入出力端子が現れず、回路図上では他のコンポーネントとは何のつながりもないように見えます。

DFB (Digital Filter Block) 自体にはタイミング発生の機能はなく、単に入力サンプルがステージング・レジスタに到着したら読み出して、何クロックかを消費してフィルタ計算を行い、結果をホールディング・レジスタに書き込んで出力データ・レディ信号を上げているだけです。

DFB は BUS_CLK をクロックとして使用しているので、指定のサンプル・レートに間に合わせるための BUS_CLK の下限が存在します。

その目安として、「Sample rate Fs (ksps):」で目的のサンプル・レートを kHz 単位で入力するようになっていて、それをフィルタ設計および「Min BUS_CLK:」の表示のために使っています。

この例では、チャネル A で 63 タップ FIR フィルタ、チャネル B で 8 次 IIR フィルタを構成していて、BUS_CLK 下限の目安は 5.856 MHz となっています。

「Filter stages:」で、このチャネルは何段で構成されるかを指定します。 複数段を指定すると、下のフィルタ・パラメタを入力するタブも複数現れます。 ここでは「1 段」を指定しているので「Stage 1」のタブのみ表示されています。

「Filter gain:」でフィルタのゲイン (LPF なら直流 (DC) でのゲイン) を指定します。

DFB の MAC (Multiply and ACcumulate unit) では 24 ビット × 24 ビットの乗算結果を 48 ビット・アキュムレータに加算するので、アキュムレータのオーバーフローに対する余裕がありません。

Filter コンポーネントのデータシートでは、フルスケールに達するディジタル信号を入力する場合には、フィルタ・ゲインを -12 dB におさえるように推奨しています。 このゲインまでなら、内部でもオーバーフローが起こらないような設定がされる、と記述されています。

4 倍オーバーサンプリングでは、アップ・サンプル時に元のサンプル列の間に 3 個の「ゼロ」を挿入するので、アップ・サンプルされたサンプル列として見ればレベルが 1/4 (-12 dB) に低下します。

それを補った上で「仕上がり」のゲインが -3 dB となるように、12 - 3 = 9 [dB] を指定しています。 今回のアプリケーションでは、周波数スイープされる単一の正弦波を入力としているので、オーバーフローについては条件は厳しくありません。

「Stage 1」のタブの中に 1 段目のフィルタのパラメタを指定する項目があります。 ここでは 1 段構成を指定しているので、Stage 2 以降のタブは現れません。

「Filter class:」でフィルタの種別を「FIR」あるいは「Biquad」のいずれかから指定します。 この例では FIR を指定しています。 ステージごとに FIR / Biquad を選べますが、ひとつのステージ内で混在させることはできません。

「Filter type:」でフィルタの周波数応答のタイプを

- Low pass

- High pass

- Band pass

- Band stop

- Sinc^4

- Hilbert

の中から選びます。

「Sinc^4」は、デルタシグマ ADC コンポーネントで使われている 4 次 CIC (Cascaded Integrator-Comb filter) デシメータの周波数応答の逆特性のフィルタです。

CIC では sinc 関数の 4 乗の特性となりますが、それと逆の特性のフィルタをかけて通過域の特性を平坦化するものです。

FIR フィルタのタップ係数計算は、一般的な等リプル近似 (Remez 交換アルゴリズムを使った Parks-McClellan 法) ではなく、窓関数法を使っています。

「Window:」の項目で Hamming / Rectangular / Blackman の中から選びます。

ハミング窓では、通過域と阻止域との間の遷移域の幅は狭くなりますが、阻止域の減衰量は小さくなります。 一方、ブラックマン窓では、遷移域の幅は広くなりますが、阻止域の減衰量は大きくなります。

この例ではハミング窓を選んでおり、阻止域の減衰量は、DC ゲインに比べて -60 dB 程度になっています。

「Filter taps:」で FIR フィルタのタップ数を選びます。 フィルタの特性によっては、タップ数の偶奇性に制約がかかることがあります。

たとえば、ヒルベルト・フィルタではタップ数が偶数の必要があり、 Sinc^4 フィルタでは奇数の必要があります。 制約に一致しない場合は警告のマークが現れ、マウス・オーバー (マウス・カーソルを重ねる) するとエラーの原因についての説明が表示されます。

「Cutoff (kHz):」の項目にカットオフ周波数を kHz 単位で入力します。 FIR LPF / HPF の場合は設定したフィルタ・ゲインから -6 dB になる周波数を指定します。

この例では LPF なのでグレイ・アウトされていますが、BPF / BEF の場合には、「Bandwidth (kHz):」の項目が現れ、パス/ストップ・バンド幅を kHz 単位で入力します。

各項目を変更して Enter キーを押すとフィルタ計算が行なわれ、右側の特性表示のグラフが変化しますが、実際のフィルタ係数の更新は「Apply」ボタンを押すか、「OK」ボタンを押して終了するまで行なわれません。

「Apply」せずに「Cancel」で抜けると、変更したフィルタ・パラメタも記憶されないので、再度カスタマイザを立ち上げても、前回の変更はなかったことにされます。 逆に言えば、パラメタをいじり過ぎてメチャメチャになった場合に、「Cancel」で抜ければ元の状態に戻ります。

次回は IIR バイクアッドの場合について説明します。