LPC810M021FN8 (7) -- SCT を PWM として使う (4)

SCT の「イベント」は、

- タイマ・カウント値とのコンペア・マッチ成立

- 入力 (CTIN) あるいは出力 (CTOUT) の、あらかじめ選択しておいた H レベル/L レベル/ライズ・エッジ/フォール・エッジのいずれかの発生

の 2 種の条件を、下のように組み合わせた

- マッチのみ

- 入出力条件のみ

- マッチと入出力条件の OR

- マッチと入出力条件の AND

4 種類のいずれかで発生させることができます。

「ステート」の関与は、そのイベントをステートごとに発生可能にするか、マスクするかの二者択一のビットマップが割り当てられているだけとなっています。

PWM への応用では、入出力条件や、ステートの関与は必要ないので、それらについての詳細は省きます。

非 UNIFY モード、つまり 16 ビット・カウンタ × 2 のモードでは、イベント発生条件に使うカウンタ/マッチ・レジスタ/ステート・レジスタの組が H 側なのか、L 側なのかを指定する必要があります。

H 側カウンタに L 側マッチ・レジスタを使って比較するようなことは (ハードウェア的に) 不可能です。

「イベント」の発生時には、次のような「動作」をさせることができます。

- カウンタのスタート (START)

- カウンタの (一時) 停止 (STOP)

- カウンタの (完全) 停止 (HALT)

- カウンタのリミット (LIMIT)

- 出力 (CTOUT) を「0」にする (CLR)

- 出力 (CTOUT) を「1」にする (SET)

- 割り込み発生

- ステート・カウンタの更新/設定

これらは、複数同時に発生させることも可能です。

「SET」動作と「CLR」動作を同時に指定すると「矛盾」が生じますが、これは後述の「コンフリクト・リゾリューション」(conflict resolution) で解決することができます。

「STOP」と「HALT」との違いは、STOP の場合には外部信号によるイベントで START 動作させ、カウントを「再開」することができますが、HALT の場合にはカウンタは完全に停止してしまい、ソフトウェアが介入してレジスタの HALT ビットをクリアしない限り、ハードウェア的にカウント再開する方法はないことです。

ステート・カウンタの操作以外は、ビットマップ、つまり、b0 がイベント 0 に対応し、b5 がイベント 5 に対応するような割り当てとなっており、そのビットが「1」の場合に対応する動作を行い、「0」の場合は「何もしない」ことを示します。

たとえば、「イベント 2」で CTOUT_0 を「SET」動作させるには、

LPC_SCT->OUT[0].SET |= (1 << 2);

のように記述します。

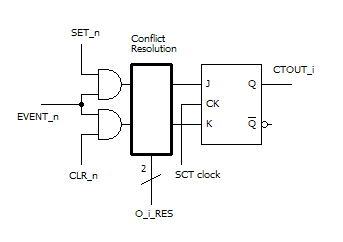

出力「i」(CTOUT_i) に対して、イベント「n」(EV_n) での SET と CLR の作用を簡略化して回路として書いた図を下に示します。

SET_n / CLR_n がそれぞれ SET / CLR 動作を許可するビットマップのビットです。

「Conflict Resolution」と書いてある「ハコ」を素通しと考えれば、JK-FF の動作から、次のクロックで出力 Q は、

- J = 0, K = 0 → Q 変化なし

- J = 1, K = 0 → Q = 1

- J = 0, K = 1 → Q = 0

- J = 1, K = 1 → Q 反転

となります。

SET = 1 / CLR = 1 の状態では「コンフリクト」が生じていて、JK-FF では出力 Q 反転という結果になるわけですが、SCT の場合には「Conflict Resolution Register」(LPC_SCT->RES) が設けられていて、各出力あたり 2 ビットの値を設定することにより、出力反転以外にも次のような動作が選択できます。

| 0x0 | 出力変化なし |

| 0x1 | SET 優先 |

| 0x2 | CLR 優先 |

| 0x3 | 出力反転 |

リセット後のデフォルトでは「0x0」になっているので、「出力変化なし」です。

この「コンフリクトが生じているのに出力変化なし」の状態には "no-change conflict" という名前が付けられていて、その条件で割り込みを起こすことができます。(LPC_SCT->CONEN)

このような割り込みが設けられているのは、

- 基本的にコンフリクトは生じるべきではない場合に、

- それでもコンフリクトが生じた場合には

- ハードウェア的には簡単に出力値を決定できないので

- 割り込みによりソフトウェアが介入して、

- エラー処理を行うなり、妥当な出力値を計算するなりして処理を続行する

ためのものであると推察されます。

コンフリクトが生じても、「優先度」でハードウェア的に出力値が決定できるなら、ソフトウェアの介入は必要なく、割り込みを起こす必要もないということだと思います。

「Single Edge PWM mode」では、(リミット値 == MATCH レジスタの値) という状態が存在し、コンフリクトが生じます。 したがって、conflict resolution については必ず考慮する必要があります。

「Double Edge PWM mode」ではコンフリクトが生じることはありません。

ディジタル・オーディオ DAC の LRCK 信号のような、デューティーが完全に 50 % である波形を発生させるためには、「出力反転機能」を使うのが最も確実な方法です。

その場合には、意図的に SET と CLR を同時にアサートしてコンフリクトを発生させ、出力反転させます。

次回に続きます。