LPC810M021FN8 (5) -- シリアル ISP (3)

リセット時に UART ISP 起動フラグと干渉しないように、外部クロック・オシレータの出力をアクティブにするのを遅らせる方式について追加の説明をします。

ブート ROM のプログラムが P0_1 をサンプリングして UART ISP の起動を判断するタイミングを外部から正確に知ることはできないため、ISP 起動の有無を 100 % 確実に行うためには、外部クロックの P0_1 への供給を「必要以上に」遅らせることになります。

つまり、ブート ROM でユーザ・プログラムの起動が決定し、実行が移ったあとでも、ユーザ・プログラムでは外部クロックを必要としているのに、まだ外部クロックが供給されていないという状態が実際に発生します。

しかし、PLL を利用してクロックを発生させている限り、問題とはなりません。

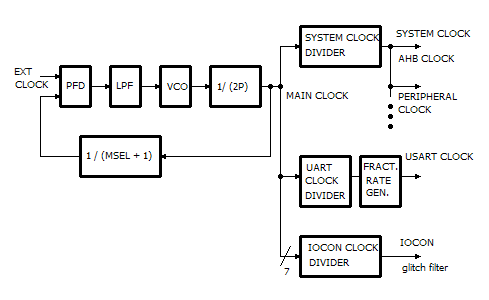

LPC8xx での PLL クロック周りの簡略化したブロック・ダイアグラムを下に示します。

この図では、PLL 入力として外部クロックを選び、「メインクロック」として PLL 出力を選んでいますが、そのマルチプレクサ部分は省略しています。

PLL を使ったクロック生成のための初期設定、再設定は (内部クロックで動作しながら) 次のような手順で行われます。

- PLL の動作停止

- PLL のパラメタ設定

- PLL 入力の選択

- PLL の動作開始

- PLL がロックするまで待つ

- メインクロックとして PLL 出力を選択

まず最初に PLL を停止しているのは、パラメタ設定は停止状態でないと有効にならないためです。

必要な設定を行ったあと PLL を動作させ、フラグを見ながらロック完了まで待ちます。

ユーザプログラム実行開始時に外部クロックが供給されていなくても、この PLL ロック完了待ちのループで外部クロックが供給され始めて PLL が正常動作になるのを (内部クロックで動作しながら) 確認してから、問題なく (PLL で逓倍された) 外部クロック動作に移ることができます。

PLL で逓倍しない「生」の外部クロックを使う必要がある場合でも、外部クロック供給確認のため PLL 設定の流れを利用し、最後に PLL 出力は使わないようにすれば外部クロック供給開始と同期が取れます。

LPC8xx では、LPC11xx とは違って、ユーザマニュアルに IRQLATENCY レジスタの記述があります。

LPC1114 の場合と同様のプログラムを使って IRQLATENCY レジスタに設定する値と、SysTick タイマのレジスタの「読み」で計測した (一定のオフセットがあると思われる) 割り込み応答クロック数の表を示します。

| SysTick 経過クロック数 (FLASH WS = 0) | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| IRQ LATENCY | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 0 〜 8 | 0.937 | 0.063 | * | * | |||||

| 9 | 0.999 | * | * | ||||||

| 10 | 0.999 | * | * | ||||||

| 11 | 0.999 | * | * | ||||||

| 12 | 0.999 | * | |||||||

| 13 | 1.0 | ||||||||

| 14 | 1.0 | ||||||||

| 15 | 1.0 | ||||||||

| 16 | 1.0 | ||||||||

下の表は、フラッシュ・メモリの読み出しウェイト・サイクル数を 1 にした場合です。

| SysTick 経過クロック数 (FLASH WS = 1) | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| IRQ LATENCY | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| 0 〜 8 | 0.239 | 0.435 | 0.282 | 0.021 | * | * | |||

| 9 | 0.765 | 0.202 | 0.033 | * | * | ||||

| 10 | 0.990 | 0.010 | * | * | |||||

| 11 | 0.999 | * | * | ||||||

| 12 | 0.999 | * | |||||||

| 13 | 1.0 | ||||||||

| 14 | 1.0 | ||||||||

| 15 | 1.0 | ||||||||

| 16 | 1.0 | ||||||||

IRQLATENCY = 13 以上で応答クロック数のバラつきがなくなっていますが、 IRQLATENCY = 12 で応答クロック数 27 となる場合があったので、この範囲をカバーするために IRQLATENCY = 14 以上にしたほうがいいかも知れません。