SH-2A 基板に AC97 コーデックをつなぐ (6)

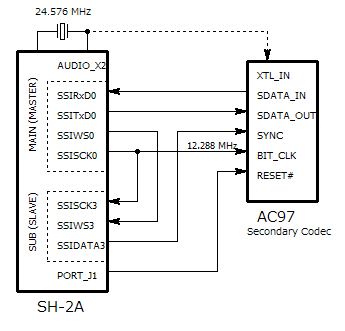

今回の実験に使っている ALC650 はプライマリ・コーデック専用で、セカンダリ・コーデックとしては使えないので試すことはできませんが、セカンダリ・コーデックとして動作させると下の図のように SH-2A 側のリソースの消費が少なくなります。

セカンダリ・コーデックの動作では、BIT_CLK は入力となるので、SSIF0 で生成した SSISCK0 を AC97 コーデック側の BIT_CLK として供給できます。

SSIF0 のオーバーサンプリング・クロックは AUDIO_X1 の 24.576 MHz を使えばよく、AUDIO_CLK 端子を犠牲にして AC97 コーデック側からクロックを入力する必要はありません。

AC97 コーデックの 24.576 MHz クロックは、BIT_CLK の作成に使われたものと同じである事が要求されるため、SH-2A 側の 24.576 MHz をコーデック側にも供給します。

コーデックに水晶振動子を直接つないで SH-2A 側とは相関のない別の 24.576 MHz を発生させたのでは、正常に動作しません。

SH-2A からコーデックの XTL_IN への接続が破線で書いてあるのは、コーデックの中には 24.576 MHz のクロックを必要とせず、BIT_CLK 入力の 12.288 MHz だけで動作する品種があり、その場合には 24.576 MHz クロックの接続が不要だからです。