アナログシンセの VCO ブロック (17) -- リニア VCO 回路(12)

ここからは、「電流反転方式」の話です。

カレント・ミラーなとで、入力電流 I のコピーの +I、-I を作り出し、タイミング・コンデンサに交互に流します。

IC 化に適しているので、 PLL IC の VCO 部などに多用されています。

基本的にコンデンサの両端の電圧は三角波となります。 のこぎり波は波形整形により得ます。

ふたつの電流を交互に流すメカニズムとしては、前に説明した

- 2コンパレータ + SR-FF

- ヒステリシス・コンパレータ / シュミット・トリガ

を利用します。

+I の積分を続け、波形の上限値に達すると FF を反転し、-I の積分に切り換えます。 そして、波形の下限値に達すると再び FF を反転し、+I の積分に戻します。

タイミング・コンデンサの電圧としては三角波となり、FF 出力は方形波となります。

原理としてはこれだけなので、実際の例を示します。

まず、PLL IC として良く知られている NE565 (LM565) およびその VCO 部だけを抜き出した NE566 (LM566) の例です。

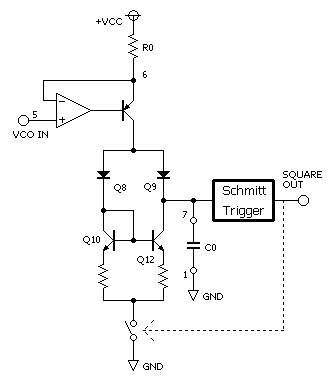

簡略化、模式化した内部回路を左に示します。 ピン番号は NE566 のものです。

上半分の OP アンプを使った定電流回路は、単に説明のためで、実際は PNPトランジスタ、 NPN トランジスタとカレントミラーの、計トランジスタ4個の回路です。

また、図のカレントミラーは簡単のために基本型の回路が書いてありますが、実際の回路は高精度なウィルソン型になっています。

この定電流回路で5ピンの電圧 に対して、

基準で電流

を

のように発生させます。

一般の VCO はグラウンド基準ですが、 基準になっているのには訳があります。

それは、PLL IC NE565 ではアナログ位相比較器として DBM (Double Balanced Modulator) を採用しているので、位相比較結果の電圧が に接続した負荷抵抗の電圧降下として表れるためです。

PLL IC の NE565 から VCO 部を抜き出した IC である NE566 も、当然そういう仕様になっています。

VCO の動作状態では、Vcc = 12 V の場合、コンデンサ (7 ピン) の電圧は 6 V 程度を中心に 2 Vp-p 程度の振幅で発振しています。

いま、この回路の下部にあるスイッチがオフでグラウンドと接続されていない状態だとします。

そうすると、Q8, Q10 側の回路は電流の行き場はないので、電流は流れません。 当然、ミラーされている Q12 側にも電流は流れません。

したがって、定電流回路からの電流 は、ダイオード Q9 を通って、7 ピンから全てコンデンサに流れ込みます。 この電流の向きを正とすると、コンデンサには

の電流が流れることになります。

この電流でコンデンサの電圧が上昇していき、シュミット・トリガの上側のスレシホールドを越えると、シュミット・トリガは反転し、この回路の下部にあるスイッチがオンとなり、グラウンドへの電流経路ができます。

そうすると、Q8, Q9 のアノード側の電圧は、Q8, Q10 の PN 接合による電圧降下とエミッタ抵抗の電圧降下を足したものとなり、2 V にも満たない電圧となります。

Q9 のカソードにつながっているコンデンサの電圧は 6 V 程度ですから、ダイオード Q9 は逆バイアスされてオフとなり、Q12 側の電流だけが流れることになります。

Q9 はオフですから、定電流回路の電流 は Q8, Q10 側に全て流れ、Q10, Q12 でミラーされて、Q12 には同じ電流

が流れます。

この電流は 7 ピンを通じてコンデンサから流れ込むことになりますから、コンデンサから見れば という電流が流れることになります。

そうすると、コンデンサの電圧は減少を始め、シュミット・トリガの下側のスレシホールドに達すると、再びシュミット・トリガが反転し、下部のスイッチがオフとなって、最初の状態に戻ります。

通常は、このように電圧入力で使いますが、5 ピンを適切な電圧に固定し、外部の定電流源から 6 ピンへ電流を流し込んでやれば、電流入力の VCO として使用することができます。

Rene Schmitz さんの web サイト (→こちら) に NE566 を使ったアナログシンセ用の VCO 回路の例があります。

PLL IC NE565 でも、位相比較部が実質的に影響しないように工夫すれば VCO 部だけ使うこともできます。